本篇文章來自:機智的互聯網

1、前言

低壓降穩壓器 (LDO) 的典型特性必然是壓降。畢竟,其名稱及其縮寫由此而來。從根本上講,壓降描述的是正常穩壓所需的 VIN 和 VOUT 之間的最小差值。

2、什么是壓降?

壓降電壓 VDO 是指為實現正常穩壓,輸入電壓 VIN 必須高出所需輸出電壓 VOUT(nom) 的最小壓差。請參見 公式 1:

公式 1:VIN ≥ VOUT(nom) + VDO

如果 VIN 低于此值,線性穩壓器將以壓降狀態工作,不再調節所需的輸出電壓。在這種情況下,輸出電壓 VOUT(dropout) 將等于 VIN 減去壓降電壓的值(公式 2):

公式 2:VOUT(dropout) = VIN − VDO

以調節后電壓為 3.3V 的 TPS799 等 LDO 為例:當輸出 200mA 電流時,TPS799 的最大壓降電壓指定為 175mV。只要輸入電壓為 3.475V 或更高,就不會影響調節過程。但是,輸入電壓降至 3.375V 將導致 LDO 以壓降狀態工作并停止調節,如圖 1 所示。雖然應將輸出電壓調節為 3.3V,但 TPS799 沒有保持穩壓所需的余量電壓。因此,輸出電壓將開始跟隨輸入電壓變化。

圖 1 在低壓降狀態下工作的TPS799

3、決定壓降的因素是什么?

壓降主要由 LDO 架構決定。 為說明原因,讓我們來了解一下 P 溝道金屬氧化物半導體 (PMOS) 和 N 溝道 MOS (NMOS) LDO,并對比其工作情況。

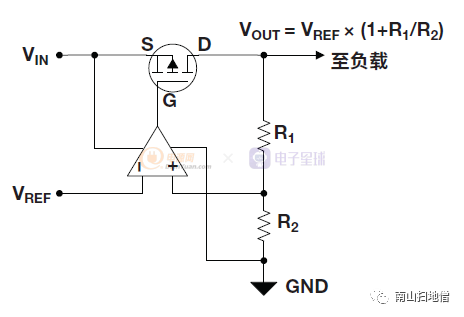

3.1、PMOS 架構 LDO

圖 2 所示為 PMOS LDO 架構。為調節所需的輸出電壓,反饋回路將控制漏-源極電阻 RDS。隨著 VIN 逐漸接近 VOUT(nom),誤差放大器將驅動柵-源極電壓 VGS 負向增大,以減小 RDS,從而保持穩壓。

圖 2 PMOS LDO

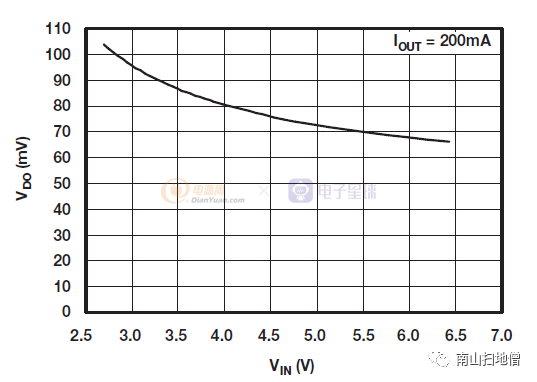

但是,在特定的點,誤差放大器輸出將在接地端達到飽和狀態,無法驅動 VGS 進一步負向增大。RDS 已達到其最小值。將此 RDS 值與輸出電流 IOUT 相乘,將得到壓降電壓。請記住,隨著 VGS 負向增大,能達到的 RDS 值越低。通過提升輸入電壓,可以使 VGS 值負向增大。因此,PMOS 架構在較高的輸出電壓下具有較低的壓降。圖 3 展示了此特性。

圖 3 TPS799 的壓降電壓與輸入電壓關系圖

如圖 3 所示,TPS799 的壓降電壓隨輸入電壓(也適用于輸出電壓)增大而降低。這是因為隨著輸入電壓升高 VGS 會負向增大。

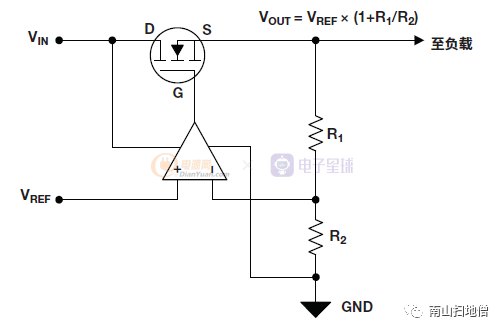

3.2、NMOS 架構 LDO

NMOS 架構如圖 4 所示,反饋回路仍然控制 RDS。但是,隨著 VIN 接近 VOUT(nom),誤差放大器將增大 VGS 以降低 RDS,從而保持穩壓。

圖 4 NMOS

LDO在特定的點,VGS 無法再升高,因為誤差放大器輸出在電源電壓 VIN 下將達到飽和狀態。達到此狀態時,RDS 處于最小值。將此值與輸出電流 IOUT 相乘,會獲得壓降電壓。不過這也會產生問題,因為誤差放大器輸出在 VIN 處達到飽和狀態,隨著 VIN 接近 VOUT(nom),VGS 也會降低。這有助于防止出現超低壓降。

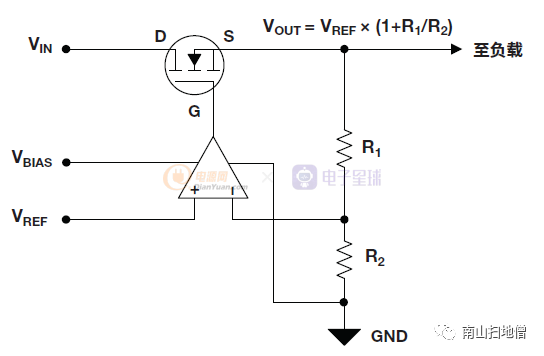

3.3、偏置 LDO

很多 NMOS LDO 都采用輔助電壓軌,即偏置電壓 VBIAS,如圖 5 所示。

圖 5 帶偏置電壓軌的 NMOS LDO

此電壓軌用作誤差放大器的正電源軌,并支持其輸出一直擺動到高于 VIN 的 VBIAS。這種配置能夠使 LDO 保持較高 VGS,從而在低輸出電壓下達到超低壓降。有時并未提供輔助電壓軌,但仍然需要在較低的輸出電壓下達到低壓降。在這種情況下,可以用內部電荷泵代替 VBIAS,如圖 6 所示。

圖 6 帶內部電荷泵的 NMOS LDO

電荷泵將提升 VIN,以便誤差放大器在缺少外部 VBIAS 電壓軌的情況下仍可以生成更大的 VGS 值。

3.4、其他因素

除了架構之外,壓降還會受到其他一些因素的影響,如表 1 所示。

表 1 影響壓降的因素

很顯然,壓降并不是一個靜態值。雖然這些因素會提高選擇 LDO 的復雜程度,但同時,還能幫助您根據特定的條件選擇最適合的 LDO。以上關于LDO基礎特性壓降部分就為大家講解完成了,喜歡的可以點個早看或者轉發哦~

------------ END ------------