首先,可控硅T在工作過(guò)程中,它的陽(yáng)極A和陰極K與電源和負(fù)載連接,組成可控硅的主電路,可控硅的門(mén)極G和陰極K與控制可控硅的裝置連接,組成可控硅的控制電路。

從可控硅的內(nèi)部分析工作過(guò)程:

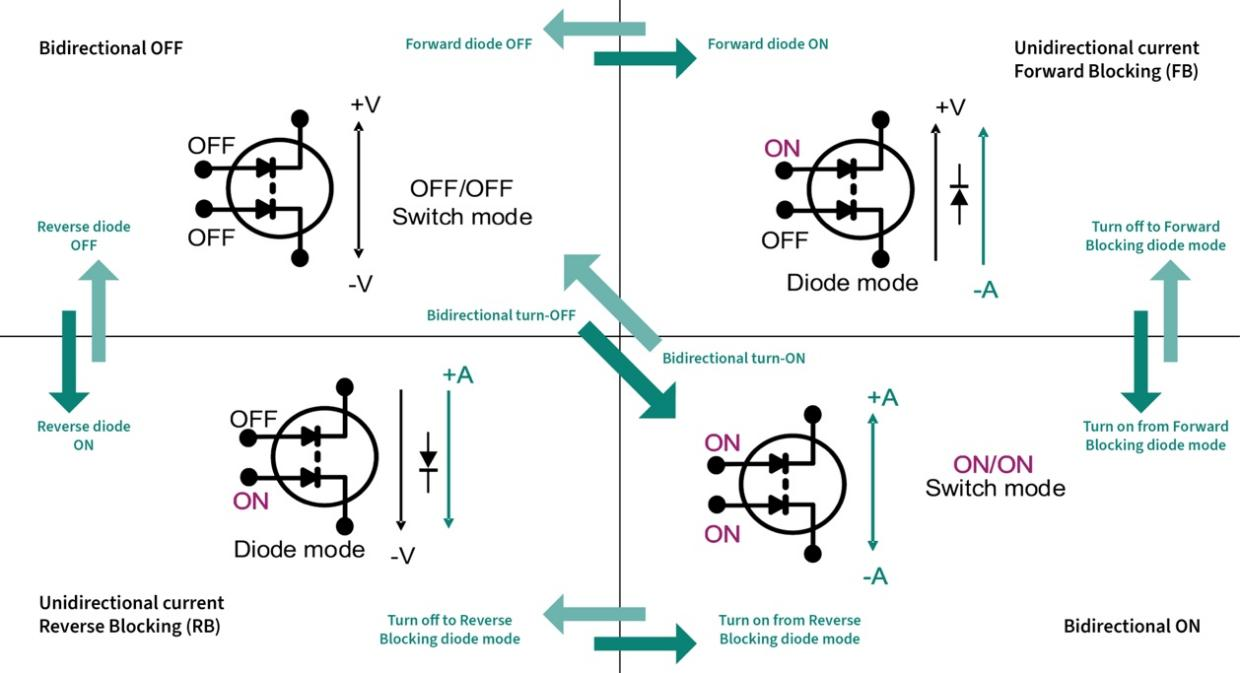

可控硅是四層三端器件,它有J1、J2、J3三個(gè)PN結(jié)圖1,可以把它中間的NP分成兩部分,構(gòu)成一個(gè)PNP型三極管和一個(gè)NPN型三極管的復(fù)合管圖2

當(dāng)可控硅承受正向陽(yáng)極電壓時(shí),為使可控硅導(dǎo)銅,必須使承受反向電壓的PN結(jié)J2失去阻擋作用。圖2中每個(gè)晶體管的集電極電流同時(shí)就是另一個(gè)晶體管的基極電流。因此,兩個(gè)互相復(fù)合的晶體管電路,當(dāng)有足夠的門(mén)機(jī)電流Ig流入時(shí),就會(huì)形成強(qiáng)烈的正反饋,造成兩晶體管飽和導(dǎo)通,晶體管飽和導(dǎo)通。

設(shè)PNP管和NPN管的集電極電流相應(yīng)為Ic1和Ic2;發(fā)射極電流相應(yīng)為Ia和Ik;電流放大系數(shù)相應(yīng)為a1=Ic1/Ia和a2=Ic2/Ik,設(shè)流過(guò)J2結(jié)的反相漏電電流為Ic0,

可控硅的陽(yáng)極電流等于兩管的集電極電流和漏電流的總和:

Ia=Ic1+Ic2+Ic0 或Ia=a1Ia+a2Ik+Ic0

若門(mén)極電流為Ig,則可控硅陰極電流為Ik=Ia+Ig

從而可以得出可控硅陽(yáng)極電流為:I=(Ic0+Iga2)/(1-(a1+a2))(1—1)式

硅PNP管和硅NPN管相應(yīng)的電流放大系數(shù)a1和a2隨其發(fā)射極電流的改變而急劇變化如圖3所示。

當(dāng)可控硅承受正向陽(yáng)極電壓,而門(mén)極未受電壓的情況下,式(1—1)中,Ig=0,(a1+a2)很小,故可控硅的陽(yáng)極電流Ia≈Ic0 晶閘關(guān)處于正向阻斷狀態(tài)。當(dāng)可控硅在正向陽(yáng)極電壓下,從門(mén)極G流入電流Ig,由于足夠大的Ig流經(jīng)NPN管的發(fā)射結(jié),從而提高起點(diǎn)流放大系數(shù)a2,產(chǎn)生足夠大的極電極電流Ic2流過(guò)PNP管的發(fā)射結(jié),并提高了PNP管的電流放大系數(shù)a1,產(chǎn)生更大的極電極電流Ic1流經(jīng)NPN管的發(fā)射結(jié)。這樣強(qiáng)烈的正反饋過(guò)程迅速進(jìn)行。從圖3,當(dāng)a1和a2隨發(fā)射極電流增加而(a1+a2)≈1時(shí),式(1—1)中的分母1-(a1+a2)≈0,因此提高了可控硅的陽(yáng)極電流Ia.這時(shí),流過(guò)可控硅的電流完全由主回路的電壓和回路電阻決定。可控硅已處于正向?qū)顟B(tài)。

式(1—1)中,在可控硅導(dǎo)通后,1-(a1+a2)≈0,即使此時(shí)門(mén)極電流Ig=0,可控硅仍能保持原來(lái)的陽(yáng)極電流Ia而繼續(xù)導(dǎo)通。可控硅在導(dǎo)通后,門(mén)極已失去作用。

在可控硅導(dǎo)通后,如果不斷的減小電源電壓或增大回路電阻,使陽(yáng)極電流Ia減小到維持電流IH以下時(shí),由于a1和a1迅速下降,當(dāng)1-(a1+a2)≈0時(shí),可控硅恢復(fù)阻斷狀態(tài)。

聲明:本內(nèi)容為作者獨(dú)立觀點(diǎn),不代表電源網(wǎng)。本網(wǎng)站原創(chuàng)內(nèi)容,如需轉(zhuǎn)載,請(qǐng)注明出處;本網(wǎng)站轉(zhuǎn)載的內(nèi)容(文章、圖片、視頻)等資料版權(quán)歸原作者所有。如我們采用了您不宜公開(kāi)的文章或圖片,未能及時(shí)和您確認(rèn),避免給雙方造成不必要的經(jīng)濟(jì)損失,請(qǐng)電郵聯(lián)系我們,以便迅速采取適當(dāng)處理措施;歡迎投稿,郵箱∶editor@netbroad.com。

| 微信關(guān)注 | ||

|

| 技術(shù)專題 | 更多>> | |

|

| 技術(shù)專題之EMC |

|

| 技術(shù)專題之PCB |