ARM是在電子電路中常見的芯片系統之一,在很多設計中都會使用ARM芯片。本文將為大家介紹ARM7當中的中斷工作模式,ARM7處理器具有2個中斷輸入,分別為IRQ中斷和FIQ中斷,如圖1所示。其對應的中斷操作模式為向量中斷IRQ模式(用于通用中斷處理)和快速中斷FIQ模式(支持數據傳輸或通道處理)。

圖1

向量中斷請求(IRQ)是一個由nIRQ輸入端的低電平所產生的正常中斷。IRQ的優先級低于FIQ,對于FIQ序列它是被屏蔽的。任何時候在一個特權模式下,都可通過置位當前程序狀態寄存器(CPSR)中的I位來禁止IRQ。

快速中斷請求(FIQ)支持數據轉移或通道處理,在ARM狀態中,FIQ模式有8個專用的寄存器可用來滿足寄存器保護的需要,這是上下文切換的最小開銷。將nFIQ信號拉低可實現外部產生FIQ。在一個特權模式中,可通過置位當前程序狀態寄存器(CPSR)中的F標志來禁止FIQ異常。當F標志清零時,ARM7處理器在每條指令結束時檢測FIQ同步器輸出端的低電平。

ARM7中斷屏蔽程序實現

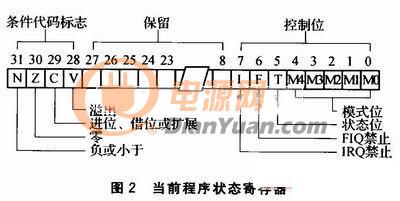

ARM7內核包含1個當前程序狀態寄存器(CPSR),該寄存器中包含條件代碼標志位、控制中斷的使能和禁止位,以及設置處理器操作模式位。當前程序狀態寄存器如圖2所示。

圖2

當前程序狀態寄存器的控制位中包含2個中斷禁止位——I和F位:當I位置位時,禁止IRQ中斷,清零時允許IRQ中斷;當F位置位時,禁止FIQ中斷,清零時允許FIQ中斷。

在ARM7系列的處理器中,只有“MRS”和“MSR”兩條指令可以直接讀取和設置當前程序狀態寄存器(CPSR)或保存程序狀態寄存器SPSR)。在ARM公司提供的C編譯器中并沒用提供特殊的語法格式,用于指定生成這兩條指令,所以如要想將IRQ中斷和FIQ中斷都屏蔽,就必須使用匯編語言來編寫函數。對于IRQ中斷,ARM還有另外一種管理模式,即通過向量中斷控制器(VIC)負責管理芯片的中斷源,如果是只屏蔽或打開向量中斷IRQ,也可以使用C語言來設計這兩個函數。

聲明:本內容為作者獨立觀點,不代表電源網。本網站原創內容,如需轉載,請注明出處;本網站轉載的內容(文章、圖片、視頻)等資料版權歸原作者所有。如我們采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯系我們,以便迅速采取適當處理措施;歡迎投稿,郵箱∶editor@netbroad.com。

| 微信關注 | ||

|

| 技術專題 | 更多>> | |

|

| 技術專題之EMC |

|

| 技術專題之PCB |