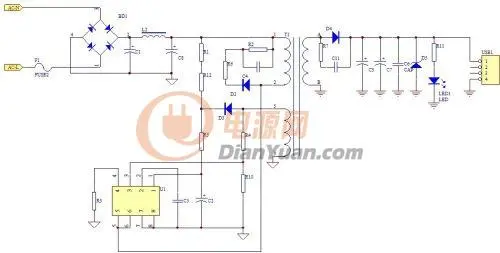

目前比較流行的低成本、超小占用空間方案設計基本都是采用PSR原邊反饋反激式,

通過原邊反饋穩壓省掉電壓反饋環路(TL431和光耦)和較低的EMC輻射省掉Y電容,

不僅省成本而且省空間,得到很多電源工程師采用。

比較是新技術,目前針對PSR原邊反饋開關電源方案設計的相關訊息在行業中欠缺。

下面結合實際來講講我對PSR原邊反饋開關電源設計的“獨特”方法——以實際為基礎。

要求條件:

全電壓輸入,輸出5V/1A,符合能源之星2之標準,符合IEC60950和EN55022安規及EMC標準。

因充電器為了方便攜帶,一般都要求小體積,所以針對5W的開關電源充電器一般都采用體積較小的EFD-15和EPC13的變壓器,此類變壓器按常規計算方式可能會認為CORE太小,做不到,如果現在還有人這樣認為,那你就OUT了。

磁芯以確定,下面就分別講講采用EFD15和EPC13的變壓器設計5V/1A 5W的電源變壓器。

1. EFD15變壓器設計

目前針對小變壓器磁芯,特別是小公司基本都無從得知CORE的B/H曲線,因PSR線路對變壓器漏感有所要求。

所以從對變壓器作最小漏感設計入手:

已知輸出電流為1A,5W功率較小,所以銅線的電流密度選8A/mm2,

次級銅線直徑為:SQRT(1/8/3.14)*2=0.4mm。

通過測量或查詢BOBBIN資料可以得知,EFD15的BOBBIN的幅寬為9.2mm。

因次級采用三重絕緣線,0.4mm的三重絕緣線實際直徑為0.6mm.

為了減小漏感把次級線圈設計為1整層,次級雜數為:9.2/0.6mm=15.3Ts,取15Ts.

因IC內部一般內置VDS耐壓600~650V的MOS,考慮到漏感尖峰,需留50~100V的應力電壓余量,所以反射電壓需控制在100V以內,

得:(Vout+VF)*n<100,即:n<100/(5+1),n<16.6,

取n=16.5,得初級匝數NP=15*16.5=247.5

取NP=248,代入上式驗證,(Vout+VF)*(NP/NS)<100,

即(5+1)*(248/15)=99.2<100,成立。

確定NP=248Ts.

假設:初級248Ts在BOBBIN上采用分3層來繞,因多層繞線考慮到出線間隙和次層以上不均勻,需至少留1Ts余量(間隙)。

得:初級銅線可用外徑為:9.2/(248/3+1)=0.109mm,對應的實際銅線直徑為0.089mm,太小(小于0.1mm不易繞制),不可取。

假設:初級248Ts在BOBBIN上采用分4層來繞,

初級銅線可用外徑為:9.2/(248/4+1)=0.146mm,對應的銅線直徑為0.126mm,實際可用銅線直徑取0.12mm。

IC的VCC電壓下限一般為10~12V,考慮到至少留3V余量,取VCC電壓為15V左右,

得:NV=Vnv/(Vout+VF)*NS=15/(5+1)*15=37.5Ts,取38Ts.

因PSR采用NV線圈穩壓,所以NV的漏感也需控制,仍然按整層設計,

得:NV線徑=9.2/(38+1)=0.235mm, 對應的銅線直徑為0.215mm,實際可用銅線直徑取0.2mm。也可采用0.1mm雙線并饒。

----------------------------------------------------------------------------------------------------------------------------------------