小弟今年大二結束,之前一直在學習單片機與FPGA,暑假無聊剛接觸逆變,有愚拙之處敬請指出。(之所以用FPGA而不用專業的SPWM驅動芯片是因為最終的項目要實現0.1°移相、0.01HZ調頻功能及其他擴展功能。(比如可能要用FPGA做光伏并網的相位、頻率跟蹤)這些是其它芯片所做不到的。)

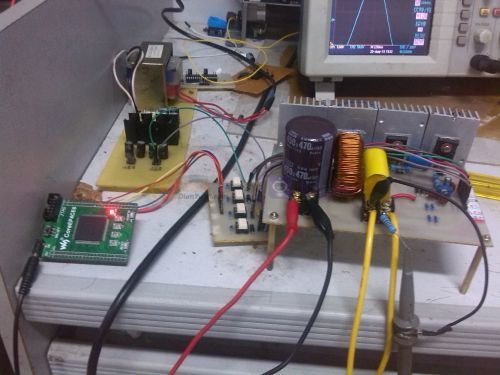

這個基于FPGA的逆變器最終是要做成三相、六路的"三相工頻測試源",三路恒流、三路恒壓,(直接市電整流濾波供電)。且電壓、電流幅值、相位、頻率均可調。 目前先把單相的給大家展示一下、原理都一樣。(三相的也還沒完成呢,主要是H橋的驅動還是有點問題,想請大家幫下下忙,問題解決完畢后我將像老壽一樣公布 所有技術資料)

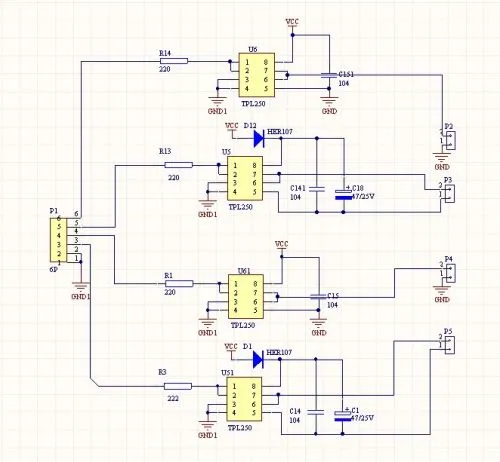

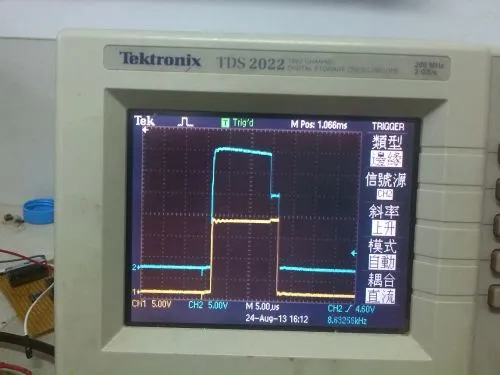

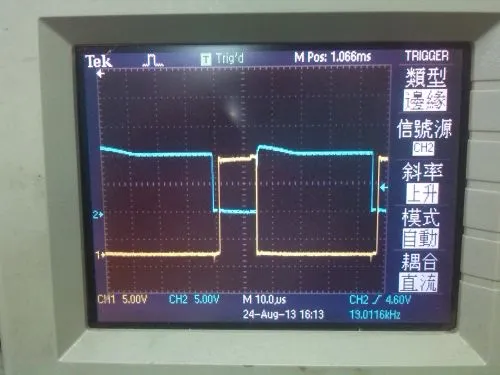

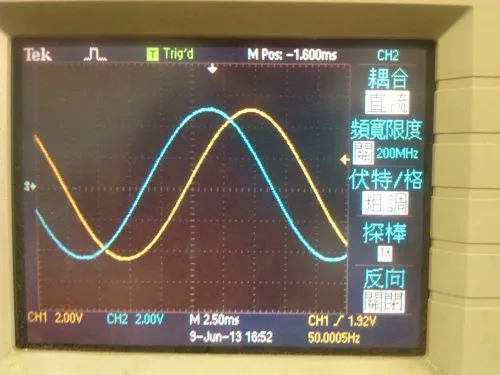

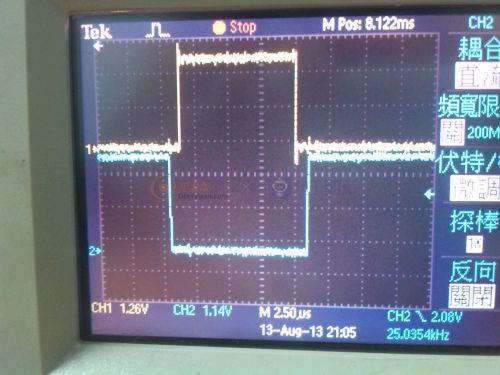

上圖為FPGA輸出SPWM波形圖,為單極性調制。邏輯控制與延時是在FPGA內部做的。輸出四路SPWM直接接上IR2110或TLP250,即可驅動后級H橋。

上圖為FPGA輸出SPWM波形圖,為單極性調制。邏輯控制與延時是在FPGA內部做的。輸出四路SPWM直接接上IR2110或TLP250,即可驅動后級H橋。

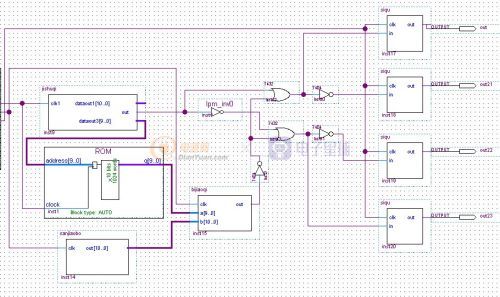

下圖為FPGA生成SPWM的結構圖(單相的,是用那種四個管子都一半高頻、一半低頻的方式調制)。

原理跟純硬件的差不多,就是將正弦波、三角波的數據先生成好放到ROM中,用兩路驅動信號分別驅動兩個模塊,再把輸出數據進行比較就生成的SPWM了。三角波和正弦波的頻率、幅值都可以很好的控制。

上圖只是說明一下FPGA產生SPWM的原理,調頻模塊直接用鎖相環替代。邏輯控制調用非門與或門,死區用程序寫的,想要多少設置多少。

上圖只是說明一下FPGA產生SPWM的原理,調頻模塊直接用鎖相環替代。邏輯控制調用非門與或門,死區用程序寫的,想要多少設置多少。

空載波形:

帶載300W波形:(波形還不錯,就是散熱片有點小,發熱有點大,不敢再加了,且發熱不均。左上管發熱最嚴重,80度左右,右下管幾乎溫的。目前此問題還沒有解決。)輸出250V,由于示波器探頭只有10倍衰減檔位所以只能看一半了。