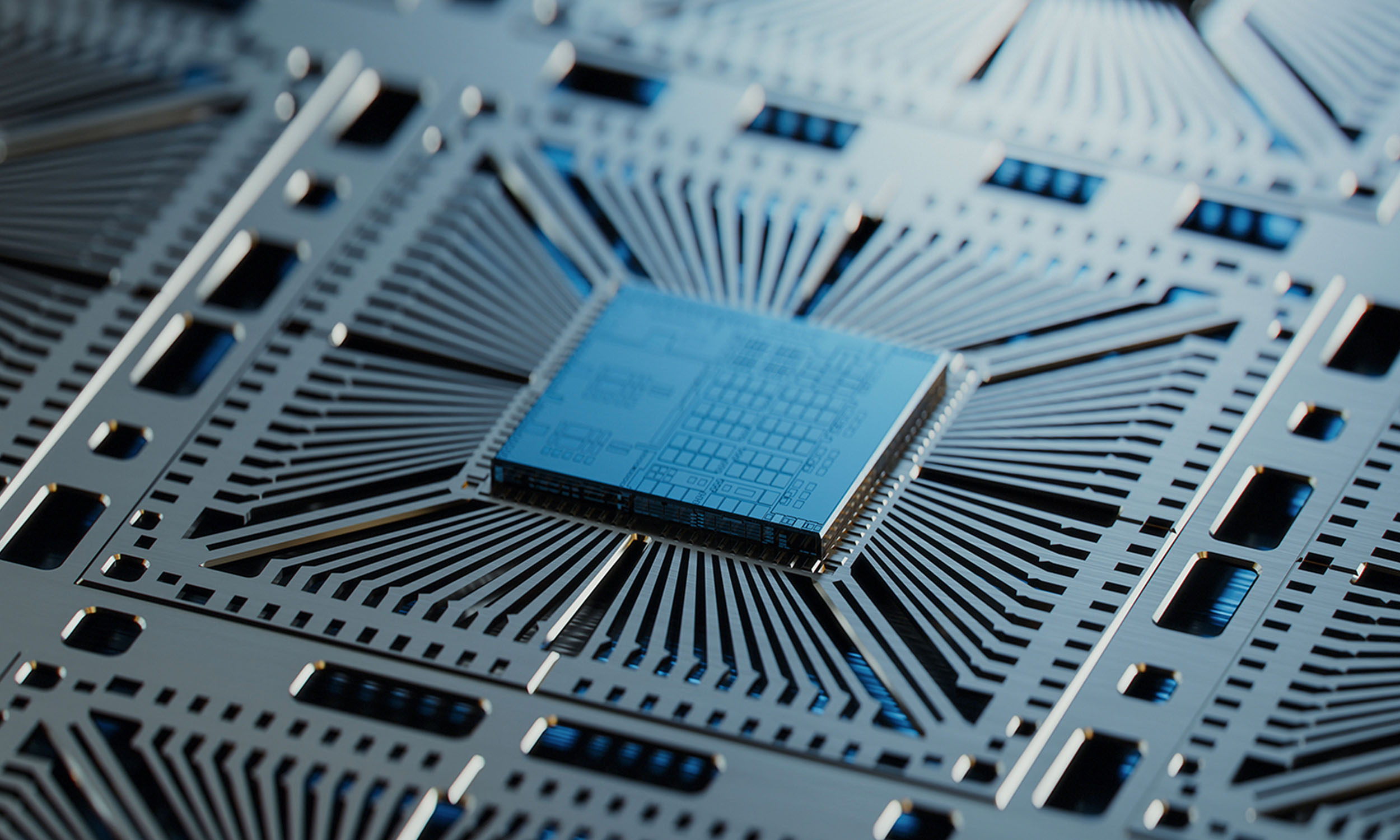

中國上海,2024 年 2 月 1 日 —— 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出 Cadence® Celsius? Studio,率先在業(yè)內(nèi)提供完整的用于電子系統(tǒng)的 AI 散熱設(shè)計(jì)和分析解決方案。Celsius Studio 可用于PCB和完整電子組件的電子散熱設(shè)計(jì),也可用于 2.5D 和 3D-IC 封裝的熱與熱應(yīng)力分析。當(dāng)前市場上的產(chǎn)品主要由不同的零散工具組成,而 Celsius Studio 引入了一種全新的方法,通過一個(gè)統(tǒng)一的平臺(tái),電氣和機(jī)械/熱工程師可以同時(shí)設(shè)計(jì)、分析和優(yōu)化產(chǎn)品性能,無需進(jìn)行幾何體簡化、操作和/或轉(zhuǎn)換。

Celsius Studio 帶來了全新的系統(tǒng)級(jí)熱完整性解決方案,將電熱協(xié)同仿真、電子散熱和熱應(yīng)力分析融合在一起。Cadence 于 2022 年收購了 Future Facilities,電氣和機(jī)械工程師現(xiàn)在可以使用一流的電子散熱技術(shù)。此外,Celsius Studio 能夠無縫地用于設(shè)計(jì)同步多物理場分析,助力設(shè)計(jì)人員在設(shè)計(jì)流程的早期發(fā)現(xiàn)熱完整性問題,并有效利用生成式 AI 優(yōu)化算法和新穎的建模算法來確定理想的散熱設(shè)計(jì)。

最終,設(shè)計(jì)人員可以簡化工作流程,改善團(tuán)隊(duì)協(xié)作,減少設(shè)計(jì)迭代,實(shí)現(xiàn)可預(yù)測的設(shè)計(jì)進(jìn)度,進(jìn)而縮短周轉(zhuǎn)時(shí)間,加快產(chǎn)品上市。Celsius Studio 具有以下優(yōu)勢(shì):

ECAD/MCAD 統(tǒng)一:設(shè)計(jì)文件無縫集成,無需簡化,工作流程更加流暢,實(shí)現(xiàn)快速高效的設(shè)計(jì)同步分析。

AI 設(shè)計(jì)優(yōu)化:Celsius Studio 中搭載了 Cadence Optimality? Intelligent System Explorer 的 AI 技術(shù),可對(duì)整個(gè)設(shè)計(jì)空間進(jìn)行快速高效的探索,鎖定理想設(shè)計(jì)。

2.5D 和 3D-IC 封裝的設(shè)計(jì)同步分析:具有前所未有的強(qiáng)大性能,輕松分析任何 2.5D 和 3D-IC 封裝,不進(jìn)行任何簡化,精確度不打折扣。

微觀和宏觀建模:小至芯片及其電源分配網(wǎng)絡(luò),大到用于放置 PCB 的機(jī)箱結(jié)構(gòu),均可進(jìn)行準(zhǔn)確建模,在市場上實(shí)屬創(chuàng)新。

大規(guī)模仿真:精確仿真大型系統(tǒng),完美還原芯片、封裝、PCB、風(fēng)扇或機(jī)殼等結(jié)構(gòu)的細(xì)節(jié)。

多階段分析:助力設(shè)計(jì)人員對(duì)設(shè)計(jì)裝配流程執(zhí)行多階段分析,解決單個(gè)封裝上多晶粒堆疊的 3D-IC 翹曲問題。

真正的系統(tǒng)級(jí)熱分析:結(jié)合有限元法(FEM)和計(jì)算流體力學(xué)(CFD),進(jìn)行從芯片到封裝,再到電路板和終端系統(tǒng)的全系統(tǒng)級(jí)熱分析。

無縫集成:與 Cadence 實(shí)現(xiàn)平臺(tái)集成,包括 Virtuoso® Layout Suite、Allegro® X Design Platform、Innovus? Implementation System、Optimality Intelligent System Explorer 和 AWR Design Environment®。

“Celsius Studio 的問世是 Cadence 開拓系統(tǒng)分析市場的一個(gè)里程碑,它不僅為芯片、封裝和 PCB 熱分析提供了理想的 AI 平臺(tái),還為電子散熱和熱應(yīng)力分析提供了卓越的 AI 平臺(tái),對(duì)于當(dāng)今先進(jìn)的封裝設(shè)計(jì)(包括chiplet和 3D-IC)而言,這類分析至關(guān)重要。”Cadence 全球副總裁兼多物理場仿真事業(yè)部總經(jīng)理 Ben Gu 表示,“Celsius Studio 與 Cadence 強(qiáng)大的實(shí)現(xiàn)平臺(tái)無縫集成,使我們的客戶能夠?qū)π酒⒎庋b和電路板乃至完整系統(tǒng)進(jìn)行多物理場設(shè)計(jì)同步分析。”

客戶反饋

“Celsius Studio 幫助三星半導(dǎo)體工程師在設(shè)計(jì)周期的早期階段獲得分析和設(shè)計(jì)見解,以更簡單的方式快速生成 3D-IC 和 2.5D 封裝的精確仿真。通過與 Cadence 的合作,我們的產(chǎn)品開發(fā)效率提高了 30%,同時(shí)優(yōu)化了封裝設(shè)計(jì)流程,縮短了周轉(zhuǎn)時(shí)間。”

- WooPoung Kim, Head of Advanced Packaging,

Samsung Device Solutions Research America

“Celsius Studio 通過 BAE Systems 的定制 GaN PDK 與 Cadence AWR Microwave Office IC 設(shè)計(jì)平臺(tái)無縫集成,能夠在整個(gè) MMIC 設(shè)計(jì)周期內(nèi)進(jìn)行快速、準(zhǔn)確的熱分析,提高了設(shè)計(jì)一次性成功的概率,并顯著改善了 RF 和熱功率放大器的性能。”

- Michael Litchfield, Technical Director, MMIC Design at BAE Systems

“借助 Celsius Studio,我們的設(shè)計(jì)團(tuán)隊(duì)能夠在設(shè)計(jì)周期的早期掌握詳細(xì)信息并開展工作,這樣就能在設(shè)計(jì)完全投入生產(chǎn)之前及時(shí)發(fā)現(xiàn)并解決散熱問題。隨著周轉(zhuǎn)時(shí)間顯著縮短,在開發(fā)這些復(fù)雜設(shè)計(jì)的過程中,Chipletz 工程團(tuán)隊(duì)能夠盡早針對(duì) 3D-IC 和 2.5D 封裝多次運(yùn)行高效且詳細(xì)的熱仿真。”

- Jeff Cain, VP of Engineering, Chipletz

可用性

了解更多 Celsius Studio 的信息,請(qǐng)?jiān)L問www.cadence.com/go/cstudiopr。有興趣參與 Celsius Studio 早期使用的客戶,請(qǐng)聯(lián)系 Cadence 客戶代表了解更多信息。

關(guān)于 Cadence

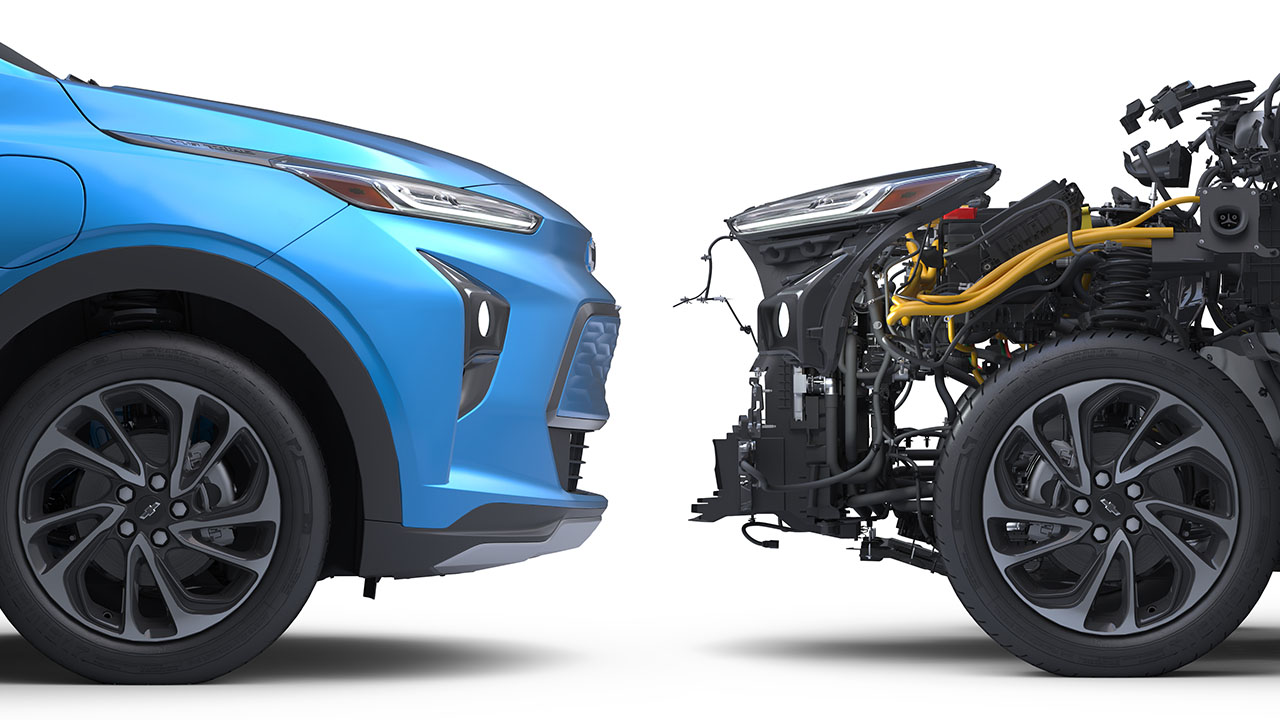

Cadence 是電子系統(tǒng)設(shè)計(jì)領(lǐng)域的關(guān)鍵領(lǐng)導(dǎo)者,擁有超過 30 年的計(jì)算軟件專業(yè)積累。基于公司的智能系統(tǒng)設(shè)計(jì)戰(zhàn)略,Cadence 致力于提供軟件、硬件和 IP 產(chǎn)品,助力電子設(shè)計(jì)概念成為現(xiàn)實(shí)。Cadence 的客戶遍布全球,皆為最具創(chuàng)新能力的企業(yè),他們向超大規(guī)模計(jì)算、5G 通訊、汽車、移動(dòng)設(shè)備、航空、消費(fèi)電子、工業(yè)和醫(yī)療等最具活力的應(yīng)用市場交付從芯片、電路板到完整系統(tǒng)的卓越電子產(chǎn)品。Cadence 已連續(xù)九年名列美國財(cái)富雜志評(píng)選的 100 家最適合工作的公司。如需了解更多信息,請(qǐng)?jiān)L問公司網(wǎng)站www.cadence.com。

聲明:本內(nèi)容為作者獨(dú)立觀點(diǎn),不代表電源網(wǎng)。本網(wǎng)站原創(chuàng)內(nèi)容,如需轉(zhuǎn)載,請(qǐng)注明出處;本網(wǎng)站轉(zhuǎn)載的內(nèi)容(文章、圖片、視頻)等資料版權(quán)歸原作者所有。如我們采用了您不宜公開的文章或圖片,未能及時(shí)和您確認(rèn),避免給雙方造成不必要的經(jīng)濟(jì)損失,請(qǐng)電郵聯(lián)系我們,以便迅速采取適當(dāng)處理措施;歡迎投稿,郵箱∶editor@netbroad.com。

| Cadence 推出突破性 DDR5 12.8Gbps MRDIMM Gen2 內(nèi)存 IP 系統(tǒng)解決方案,助力云端 AI 技術(shù)升級(jí) | 25-05-07 11:23 |

|---|---|

| 瑞芯微 RK2118 集成 Cadence Tensilica HiFi 4 DSP 提供強(qiáng)大的音頻處理 | 25-04-22 16:15 |

| Cadence 率先推出 eUSB2V2 IP 解決方案,助力打造高速連接新范式 | 25-04-15 15:02 |

| Cadence 利用 NVIDIA Grace Blackwell 加速 AI 驅(qū)動(dòng)的工程設(shè)計(jì)和科學(xué)應(yīng)用 | 25-03-24 15:34 |

| Conformal AI Studio 可將 SoC 設(shè)計(jì)師的效率提升 10 倍 | 25-03-20 15:33 |

| 微信關(guān)注 | ||

|

| 技術(shù)專題 | 更多>> | |

|

| 技術(shù)專題之EMC |

|

| 技術(shù)專題之PCB |