設計中,根據(jù)IXYS公司IXFN50N80Q2芯片手冊中提供的ID-VDS,ID-VGS和Cap-VDS等特性曲線及相關參數(shù),利用saber提供的Model Architect菜單下Power MOSFET Tool建立IXFN50N80Q2仿真模型,圖1所示MOSFET DC Characteristics設置。

圖2所示MOSFET Capacitance Characteristics設置,Body Diode參數(shù)采用默認設置。

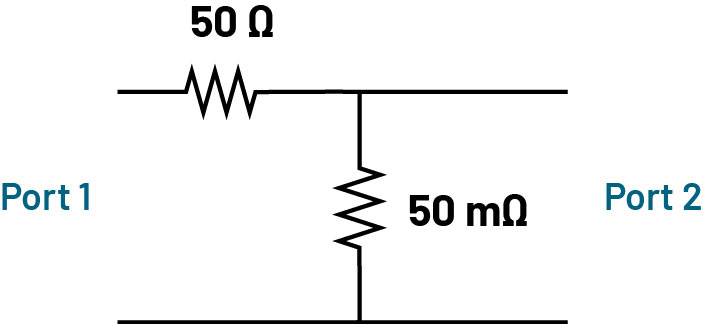

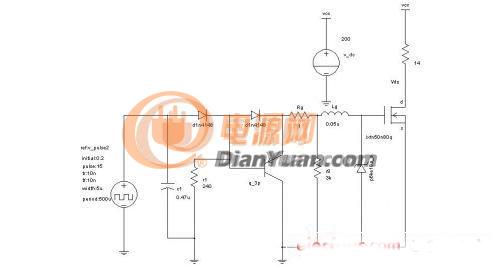

首先驗證Rg、Vgs、Vds關系,仿真電路如圖。

圖1

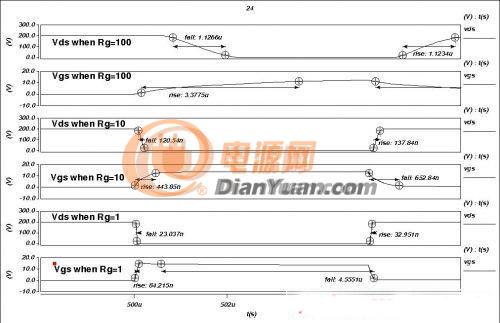

這里電路中加入了一定的電感Lg,仿真電路寄生電感,取值是0.05uH,有沒有什么依據(jù)?當時是想導線計算電感的時候好像是要加上0.05u,就放了個0.05u。仿真過程是,Rg分別取1歐姆,到10歐姆,到100歐姆。驗證Rg取值對驅動波形Vgs和開關導通特性Vds影響。結果如下圖2:

圖2

可以看出,不同Rg阻值對MOSFET IXFN50N80Q2的影響。設計中,取Rg=10,取Rg=1,擔心過沖擊穿Vgs,取100,上升沿速度太慢,不滿足高速應用。

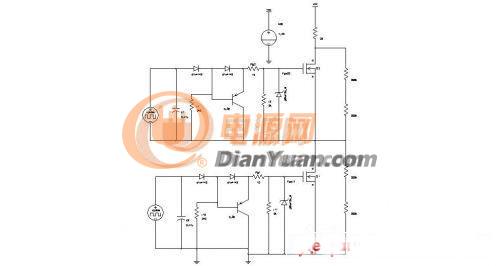

下邊討論MOSFET串聯(lián)問題。仿真電路如圖:仿真電路中兩路驅動,只有Rg參數(shù)不一致,其他均一致。

圖3

Q2的驅動電路中Rg=15,Q1的驅動電路中Rg=10,這樣的目的是在討論驅動電路中等效電阻的不一致(可能來自Rg本身不一致,也可能是線路不同,器件不同而造成的不一致)情況下,對串聯(lián)MOSFET導通過程影響。觀察Vd1和Vd2兩點的波形,如圖:

圖4

從圖中可以明顯看到,由于驅動電路參數(shù)不一致Rg1

一般MOSFET串聯(lián)都需要動態(tài)和靜態(tài)均壓。靜態(tài)均壓見圖中的MOSFET兩端并聯(lián)電阻,取值可以參考MOSFET手冊中關斷狀態(tài)的漏電流,通過靜態(tài)電阻的漏電流是通過MOSFET靜態(tài)漏電流的6倍左右,太大會加大電阻靜態(tài)損耗。

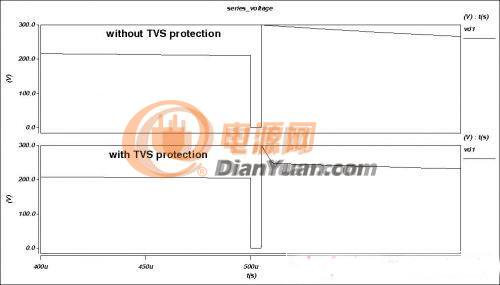

本設計中動態(tài)均壓網絡,采用TVS并聯(lián)在MOSFET兩端,起到保護作用。TVS管好像有點貴,也可以采用RCD網絡。有人說,TVS并聯(lián)起到的不是動態(tài)均壓作用,只是瞬態(tài)保護作用,這也是有道理的。

TVS管選擇,就是Vwm大于電路正常工作電壓,Vc小于電路額定最大工作電壓。

采用TVS管保護電路前后,Vd1仿真波形對比圖:

圖5

可以看到,加入TVS管后,尖峰脈沖的持續(xù)時間大大縮短。

MOSFET串聯(lián)應用,在保證動態(tài)靜態(tài)均壓和驅動一致性的條件下,還要采用一些隔離技術和多路驅動技術,以保證多只MOSFET串聯(lián)組成高壓大功率高頻開關。這方面這里就不再寫了,希望大家指點

聲明:本內容為作者獨立觀點,不代表電源網。本網站原創(chuàng)內容,如需轉載,請注明出處;本網站轉載的內容(文章、圖片、視頻)等資料版權歸原作者所有。如我們采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯(lián)系我們,以便迅速采取適當處理措施;歡迎投稿,郵箱∶editor@netbroad.com。

| 微信關注 | ||

|

| 技術專題 | 更多>> | |

|

| 技術專題之EMC |

|

| 技術專題之PCB |