大家好,我是電源漫談,很高興和各位一起分享我的第69篇原創文章,喜歡和支持我的工程師,一定記得給我點贊、收藏、分享。

前述文章,PowerSmart™ DCLD設計電壓模式BUCK數字補償器 ,我們詳細測試了BUCK電路在電壓模式下的BODE圖,本文通過進一步優化其環路特性以達到更優的閉環特性,考慮到篇幅所限,此處僅作部分波形結果記錄。

一.原始狀態的環路BODE圖及相關時間參數

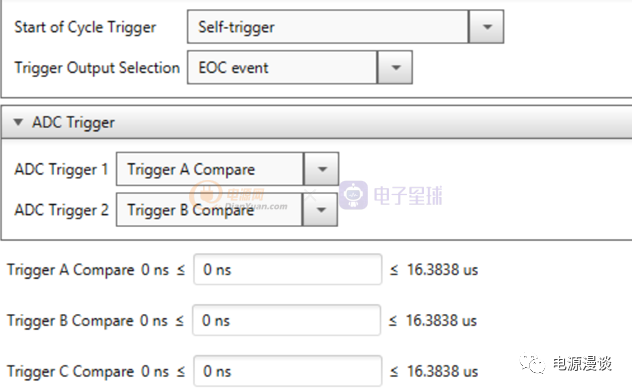

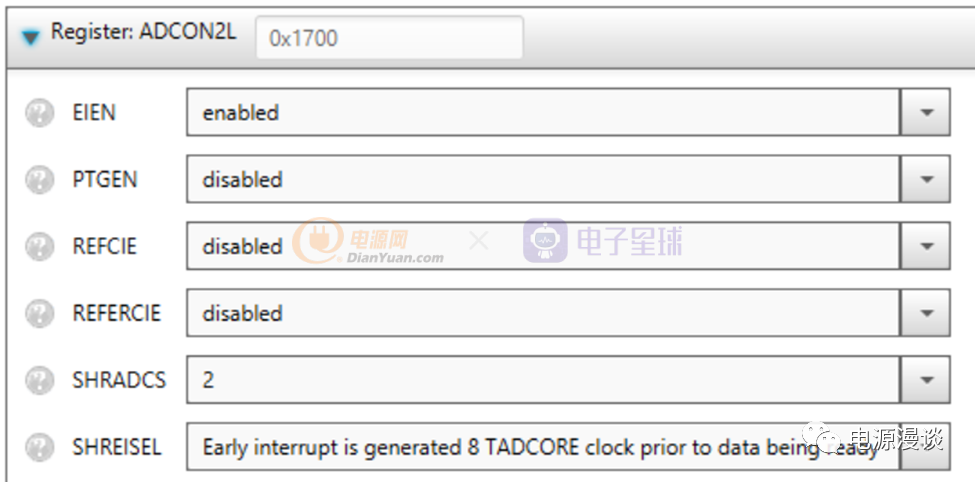

圖1 目前ADC的時鐘源及分頻1設置

圖2 目前ADC的分頻2設置

在目前狀態下,我們選擇FOSC/2為ADC時鐘源,FOSC設置為最大主頻100MIPS,FOSC對應200M,測試DEMO上使用的是共享內核的ADC CORE采樣輸出電壓和輸入電壓,可知ADC的共享內核設置為了50M,這是一個相對保守的ADC時鐘設置。

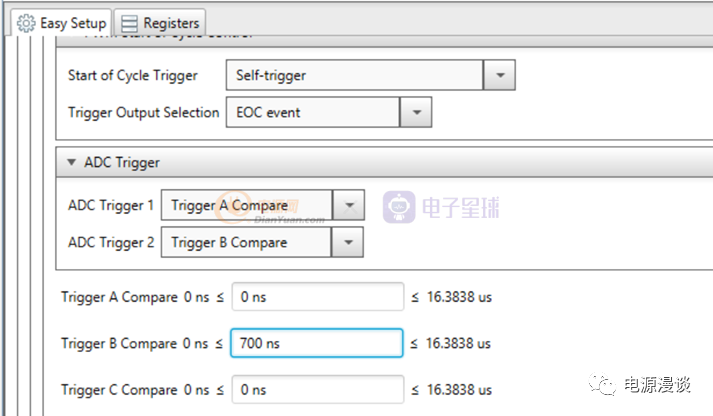

圖3 目前的觸發設置

TRIGA用來觸發AN12輸入電壓信號,TRIGB用來觸發AN13輸出電壓反饋值,此時觸發信號都是0時刻。

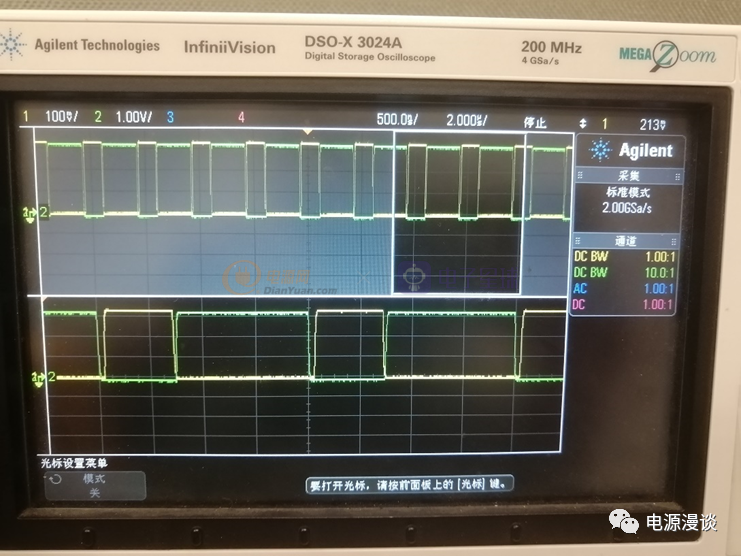

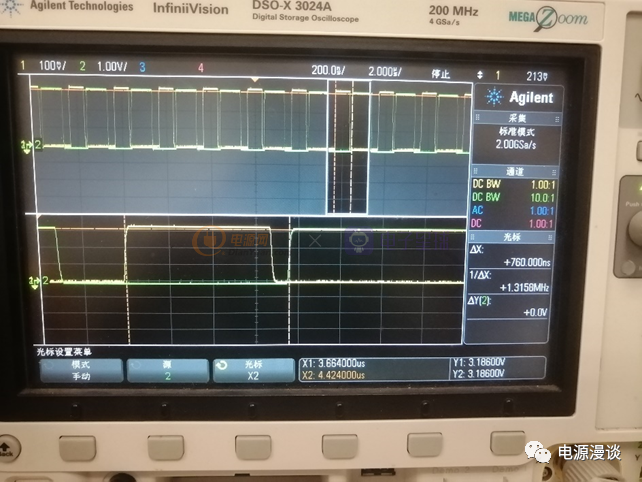

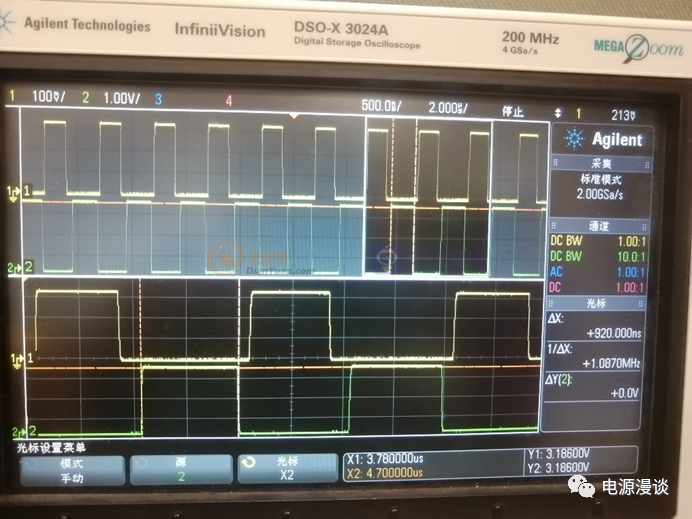

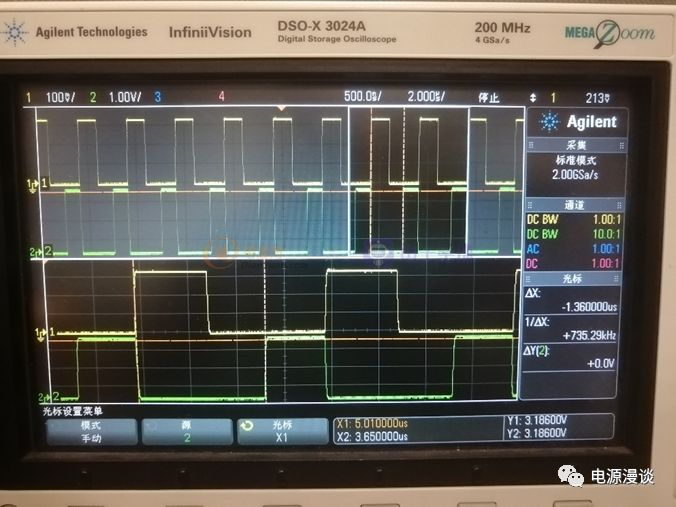

圖4 BUCK上下開關管的驅動波形

從上圖看,我們將PWM1H上升沿死區設置的偏大一些。

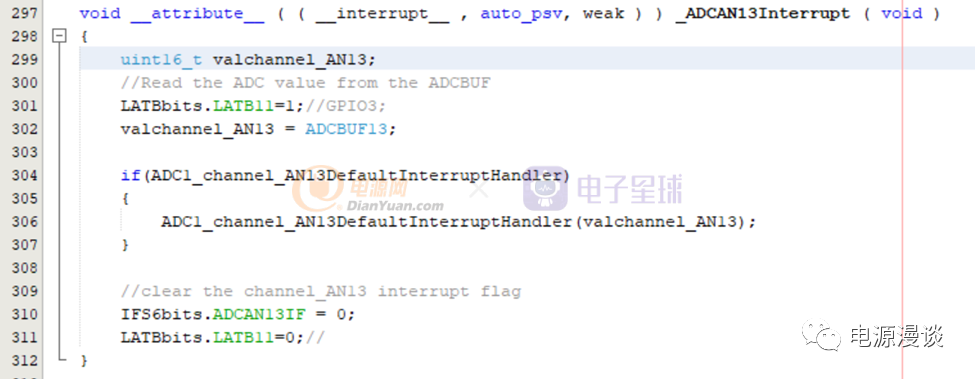

圖5 從觸發時刻到進入ADC中斷的延時

此處由于采用共享內核去做ADC采樣轉換,且會先采樣轉換AN12輸入電壓信號,因此看起來進入AN13 的ADC中斷采樣轉換延時偏大,達到960nS,在實際應用中可采用專用內核去做輸出電壓的采樣,且實施早中斷等措施減小采樣轉換延時。

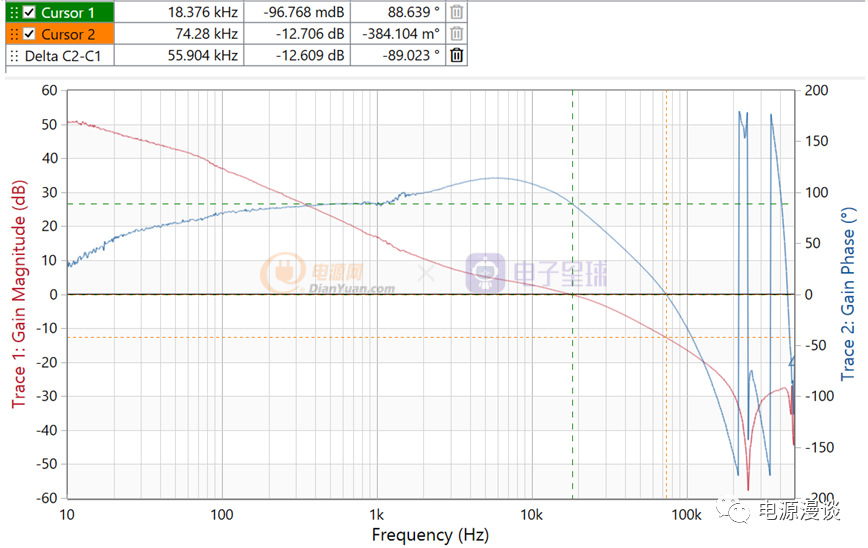

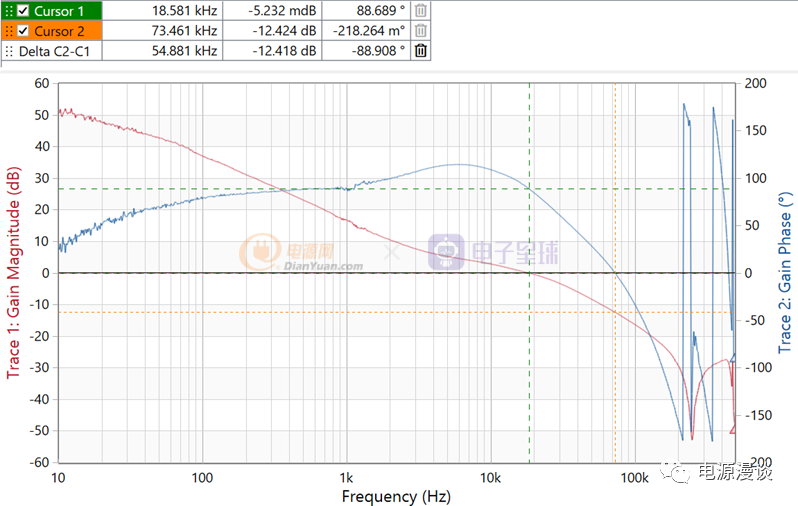

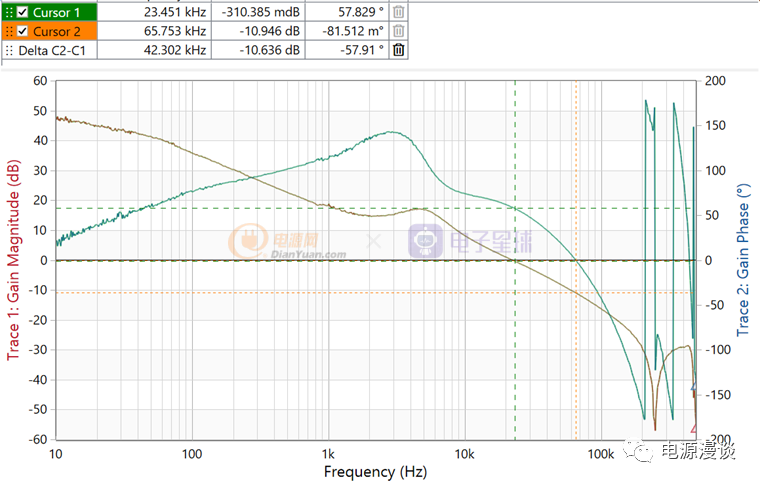

圖6-1 輸入為9V輸出3.3V時空載的閉環BODE圖

可知穿越頻率18.3k,相位裕度88.6C,增益裕量12.7db。

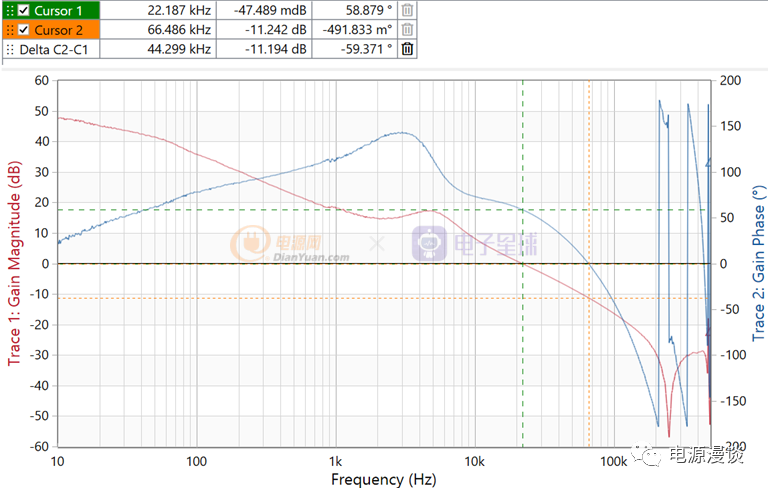

圖6-2 輸入為9V輸出3.3V時滿載的閉環BODE圖

此處DEMO滿載電流比較小,僅有1A,如圖6中,滿載的環路特性為,穿越頻率22.18k,相位裕度58.8C,增益裕量11.2db。從筆者實測的空載和滿載的環路曲線上看,按照目前的環路補償器參數設置,基本是一個穩定的環路曲線。

二.ADC早中斷設置的影響

圖7 ADC早中斷設置1

圖8 ADC早中斷設置2

圖9 ADC早中斷實施后對采樣延時的影響

從上述圖9的波形上看,對于AN13采樣轉換實施ADC8個Tad的早中斷后,AN12,AN13的總采樣轉換延時減小約200ns。

圖10 實施AN13的早中斷后的空載環路BODE圖

可知穿越頻率18.58k,相位裕度88.69C,增益裕量12.42db。

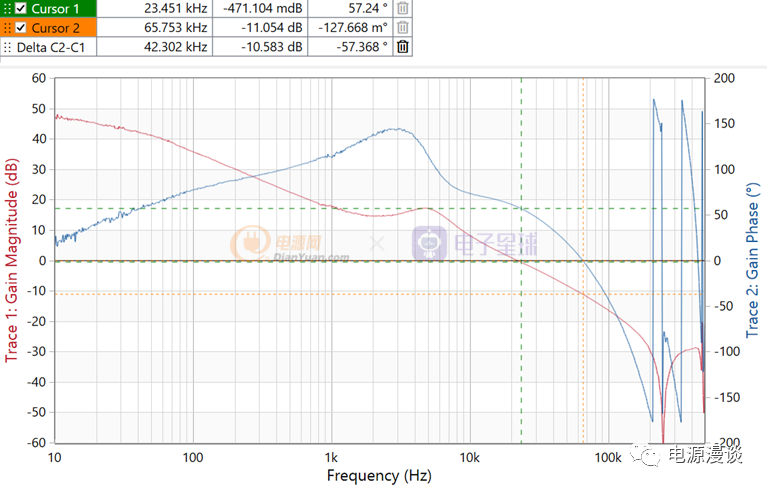

圖11 實施AN13的早中斷后的滿載環路BODE圖

滿載的環路特性為,穿越頻率23.45k,相位裕度57C,增益裕量11db。此種情況下早中斷對環路特性影響不是很明顯。

三.改善反饋信號ADC觸發位置的影響

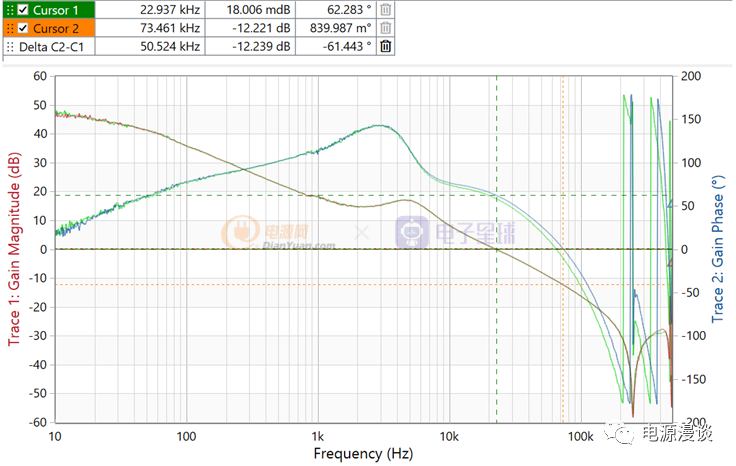

后面的測試,我們僅僅對比滿載時的環路曲線,將增加ADC早中斷的情況下的BODE圖放置在這里,作為背景,如圖12所示。

圖12 實施AN13的早中斷后的滿載環路BODE圖

圖13 目前整個ADC中斷的執行時間測量設置

圖14 目前整個ADC中斷的執行時間測量

從圖14來看,目前主頻100MIPS配置下,電壓模式三型補償器環路設計配置下的ADC中斷執行時間為920nS。

圖15 測量電壓模式三型補償器單獨執行時間

圖16 測量電壓模式三型補償器單獨執行時間

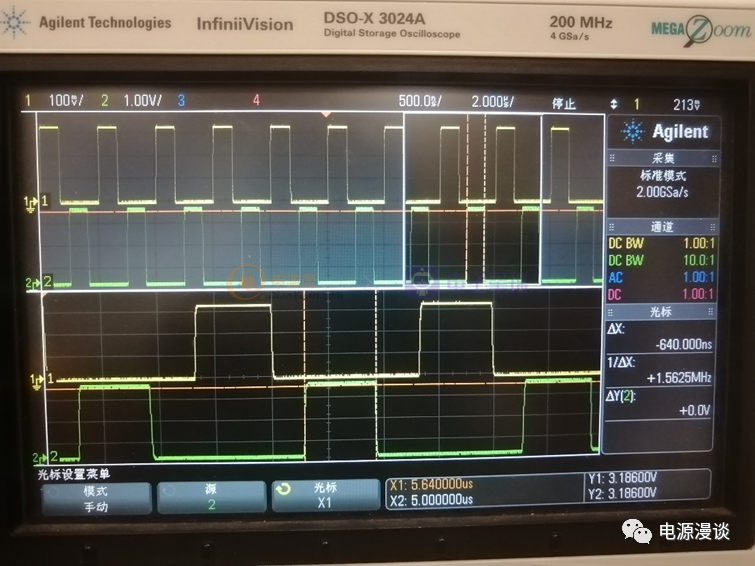

從圖16來看,目前主頻100MIPS配置下,三型補償器的執行時間為640nS。

圖17 AN13 觸發時間后移測試

圖18 AN13的ADC觸發位置后移后的波形

如圖18中,CH1為PWM1H波形,CH2為I/O在ADC中斷中的翻轉標志,從圖上看,后移AN13的觸發位置后,離開ADC中斷后不需要等待,通過立即更新設置讓環路計算結果作用以改變電壓模式控制的控制量占空比。

圖19 改善AN13觸發位置后的滿載BODE圖

從實測波形看,適當改變AN13的觸發位置后,可以看到相位裕量有了明顯提升,帶寬為23k,相位裕量62C,增益裕量12.2db,相比背景增加了5C左右。

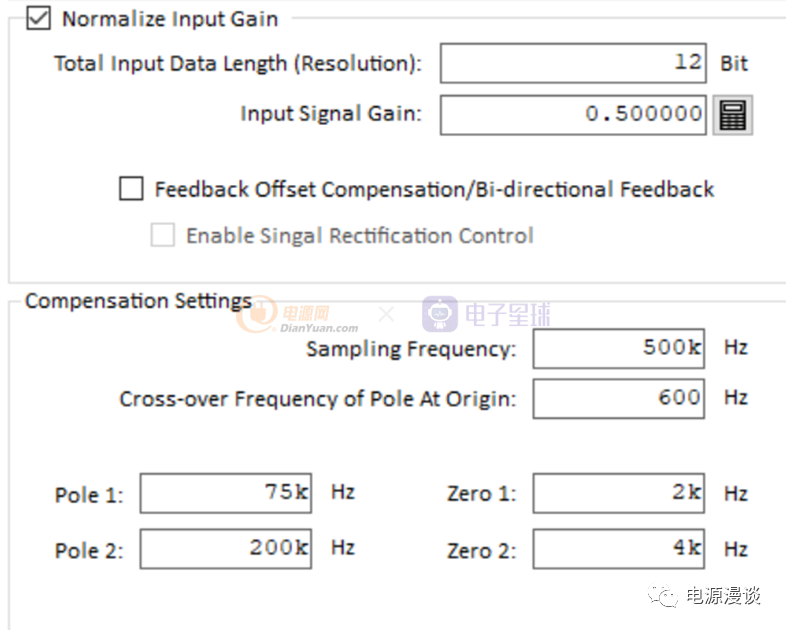

圖20 目前PowerSmart DCLD中的零極點設置

基于目前的PowerSmart DCLD中的零極點設置,由于提升了相位裕量,我們可以進一步提高增益曲線,所以將零頻率極點改為700Hz。

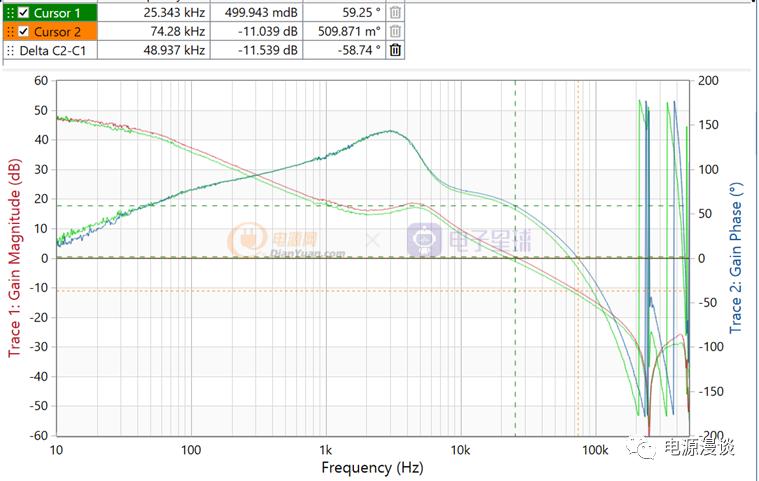

圖21 改變觸發位置及零頻率極點位置后的環路BODE圖

從實測曲線圖21所示,相比背景曲線,通過改變反饋信號的ADC觸發位置及補償器零頻率極點位置,有效增加了帶寬并且增加了相位裕量。目前測試得到的環路參數為,穿越頻率為25kHz,相位裕量60C,增益裕量11db,這已經是一個相對較完美的環路特性,帶寬達到1/20的開關頻率500kHz的值,且相位裕量和增益裕量足夠。