逆變器的工作方式和原理相信大家都比較熟悉了,我也是最近幾年在電源網逆變論壇的引導才涉足這個圈子的。為什么說這是一個圈子呢?因為它有著和其它開關電源不同的“生活區”。

近幾年火爆的LED電源就像生活在霧霾都市里的北京人一樣,快節奏工作的同時也在不斷創新(減排),基本的拓撲都是APFC+LLC或APFC+QR,隨著功率需求不斷提高,單級PFC架構的也慢慢消亡,上次還偶然看到了APFC+LCC產品。

一直充實著民用市場的充電器和適配器更是時刻與國際掛鉤,適應全電壓輸入的同時,對效率和功耗的要求也是不斷在更新,采用BUCK PFC+LLC+SR的產品也偶爾浮現。

在這些“其它開關電源”行業,近幾年出現的新方案拓撲可謂是層出不窮:PSR、交錯PFC、BUCK PFC、LCC、LLC……

連載目錄:

- 交錯控制電路詳解

- 輸入電壓溫控詳解

- 前級全橋驅動詳解

- 前級全橋升壓詳解

- 后級H橋變流詳解

- 后級H橋驅動詳解

- 整機輔助電源詳解

這幾天陸續把這些完成,歡迎大家關注、收藏,不迷路。有問題可以發評論,我會盡量回答大家。

交錯控制電路詳解

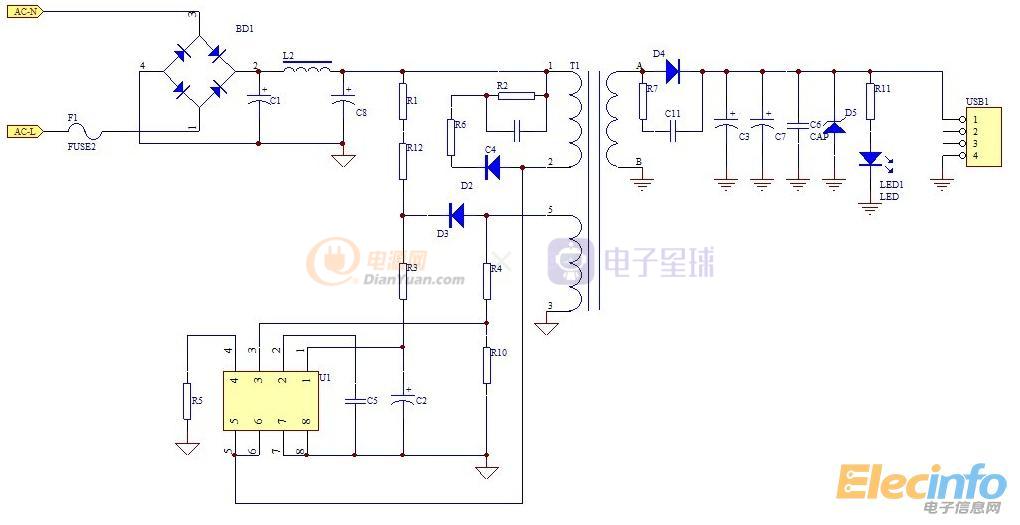

典型的PSR電路

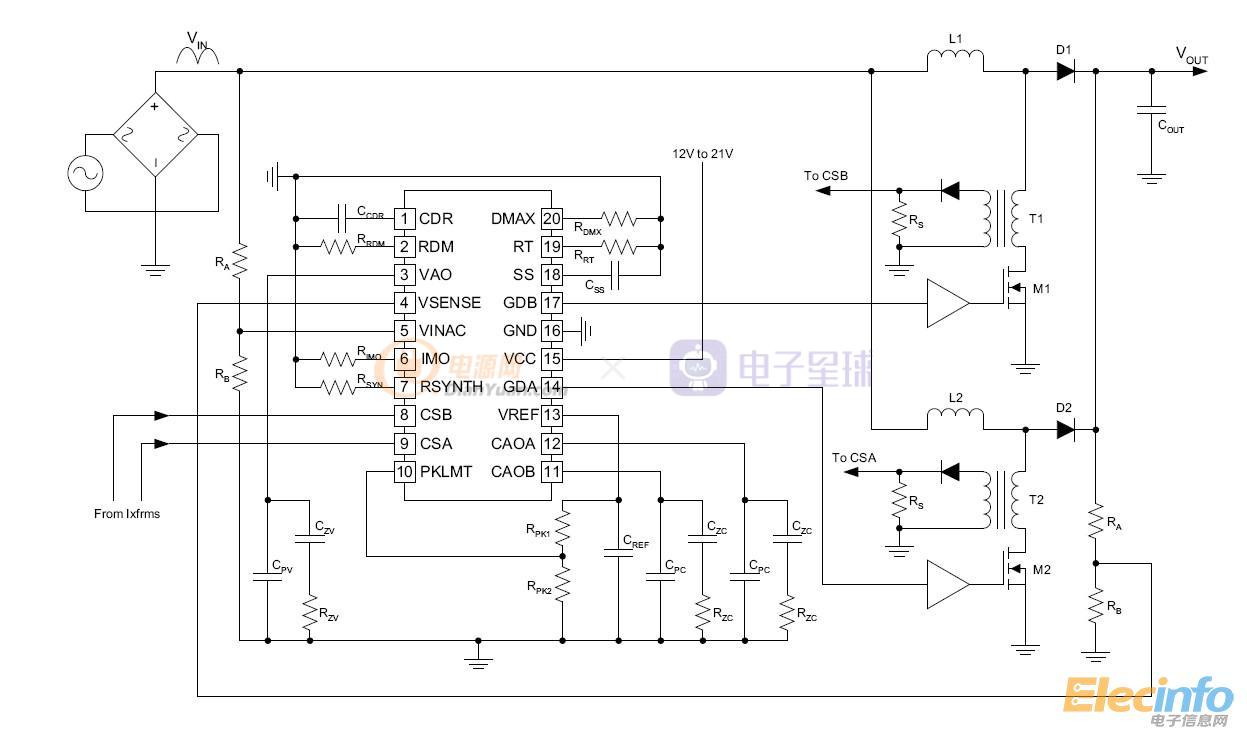

典型的交錯PFC電路

典型的BUCK PFC電路

典型的LLC電路

LCC電路架構圖

這些新的拓撲你做過的有多少?

再看看目前的逆變器行業,基本都還是用著比行業工程師平均年齡還老的方案和拓撲,就像生活在深山區里的勤人一樣,有著自然的清新空氣(風光太陽能市場),有著不必創新而能持續的生活法則。

市場上千篇一律的傳統推挽、傳統全橋甚至工頻方案的逆變器。是什么阻礙了逆變器新技術的發展?

是那幾十上百A的電流導致設計上的局限嗎?導致電流應力、功率裕量、損耗、偏磁=等設計上的困難?100A左右的電流看起來是不小,但也不至于恐怖吧。

其實我們日常經常接觸到這么大電流的產品,只是大家不覺得,電腦的主板CPU供電和顯卡的GPU供電電流都是100A+,甚至高達幾百A。

目前據說有顯卡單卡耗電800W的“電老虎級”專業顯卡,按照現在的GPU核心電壓1.0V來計算,GPU的供電電流有700+A了\,雙卡SLI電流高達1500A+,更恐怖的是普通主板已經支持4路的SLI,顯卡耗電流可以達到3000A+。

某品牌主板的37相供電(CPU供電32相交錯+CPU內置GPU供電3相交錯+VTT供電2相交錯。我一直在尋找最適合逆變器的工作拓撲,也做了大量的仿真了和實驗。

目前大家常用的多變壓器架構還是初級并聯次級串聯式的推挽架構,這種架構在變壓器一致性存在偏差時的影響是不容忽視的,而變壓器幾乎不可能完全一致。

現在LED電源上用得火爆LLC架構又不適合逆變器輸入電瓶端的寬范圍電壓,需與BOOST配合使用。最后還是想到了電腦CPU和GPU供電電源交錯控制,回想起來10年前的電腦主板CPU供電就是3-4相交錯式BUCK控制的,現在高端主板的CPU和顯卡的GPU供電都達到32甚至64相交錯供電了,顯卡單卡64相交錯,4卡3000A的電流算下來每相也就10A多點了。

讓我不明白的是10年前就已經有交錯架構的拓撲在應用,雖然BUCK和全橋是有區別,但交錯控制原理基本還是一樣的,為什么這10多年在電流應力也較大的逆變器行業沒有得到廣泛的應用呢?交錯控制使得再大的電流都不再恐怖了,如果使逆變器可以像顯卡組SLI一樣,實現直接并聯那就完美了。

接下來在交錯推挽和交錯全橋上也做了些考量和選擇,即使是交錯式推挽,還是無法避免不對稱導致的偏磁,所以準備先拿交錯全橋來小試牛刀。

多變壓器交錯式并聯與初級并聯次級串聯方式的對比,我會寫另外一篇文章。

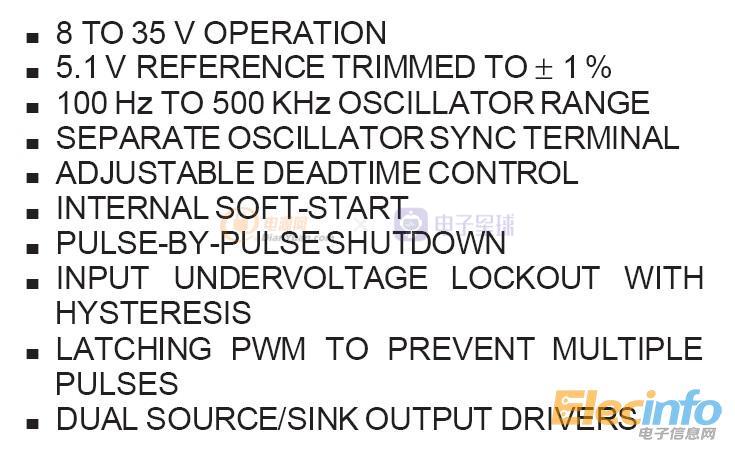

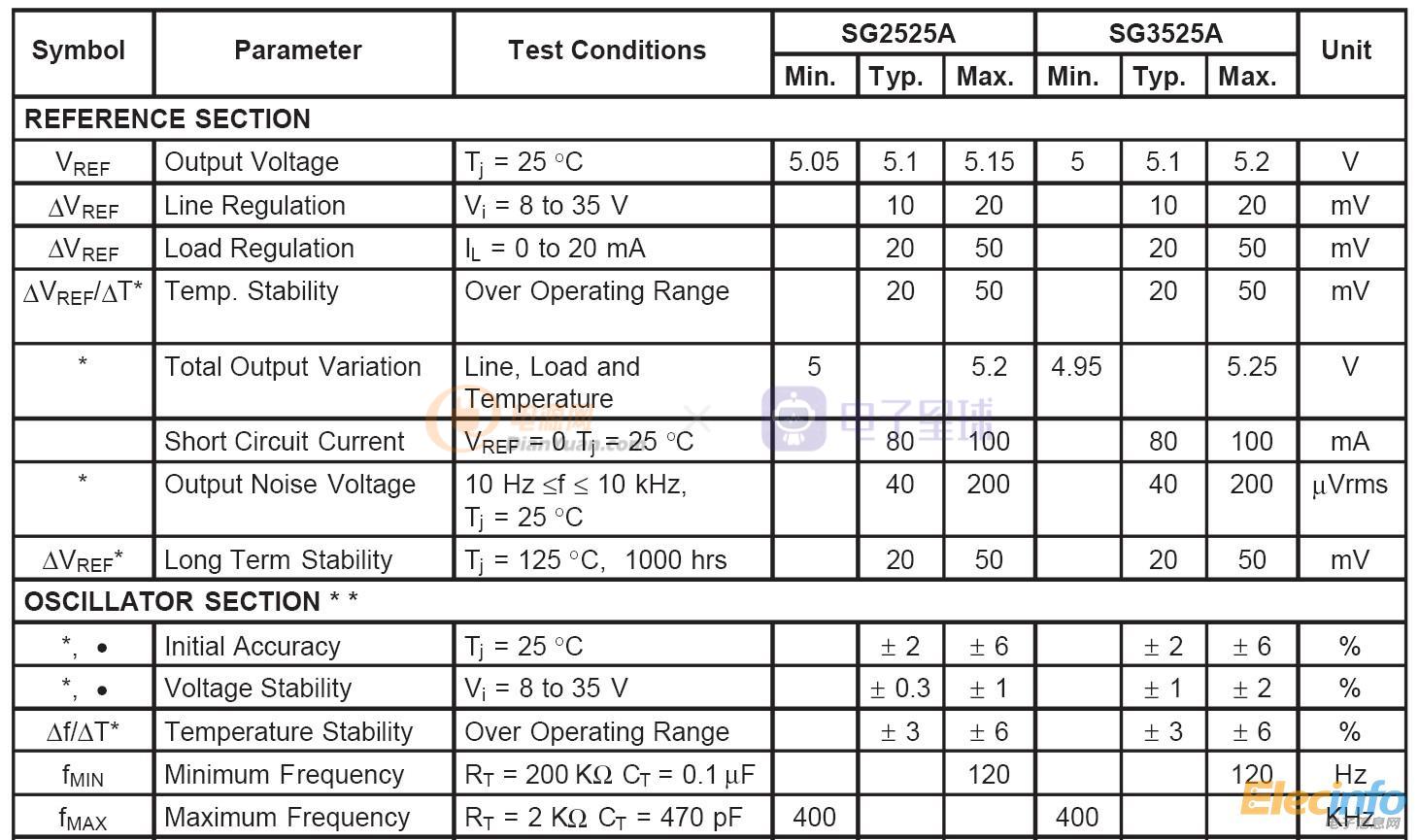

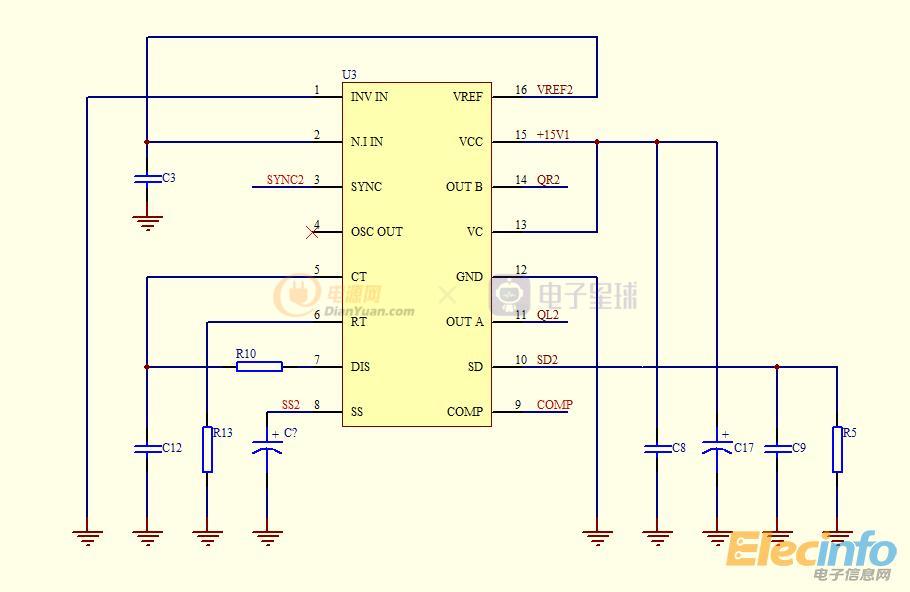

PWM控制IC首選還是大家熟知的SG3525,在這里我選擇ST的SG3525A。

相比其他的控制器,它的優點有:

1. 雙端最大占空比可以達到98%(實際在30-35K的頻率下實測也的確可以達到97~98%之間),這點對開環效率影響還是比較可觀的,部分其他品牌的SG3525標稱卻只有96%。

2. 有同步控制端,可直接級聯或交錯控制,省去了外置穩定的三角波電路控制的麻煩。

3. 最大工作頻率可以達到500KHz。規格書的首頁標稱的最大工作頻率可以達到500KHz,當然實際測試也是可以達到的,只是需要加些外圍電路讓死區時間為0。在規格書的詳細參數中標稱卻是400KHz,但在交錯控制時,同步端的輸入信號卻又不支持500KHz,所以這個500KHz真心覺得是個忽悠,但這對實現多相級聯式交錯非常有用,400KHz實現一般的逆變器(30-35KHz 開關頻率)4相交錯還是沒問題的。

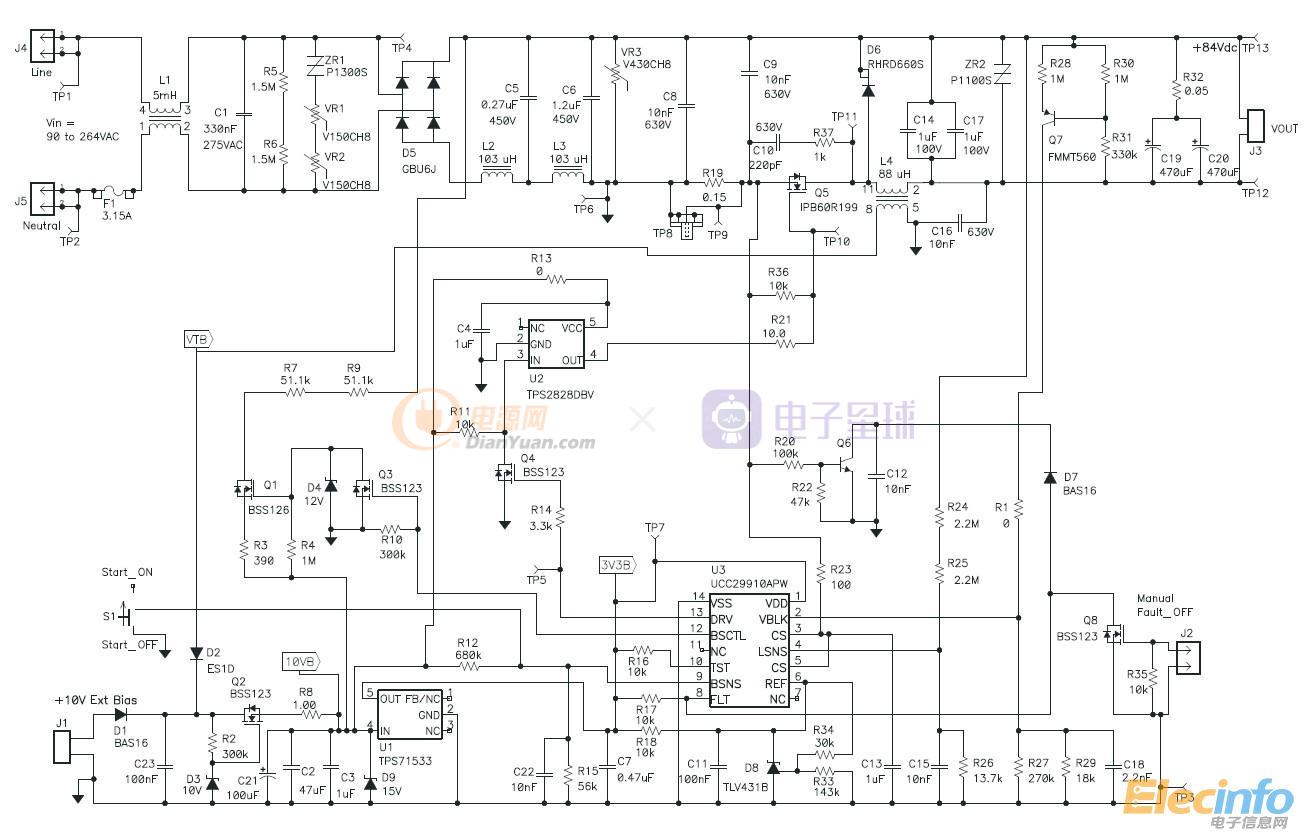

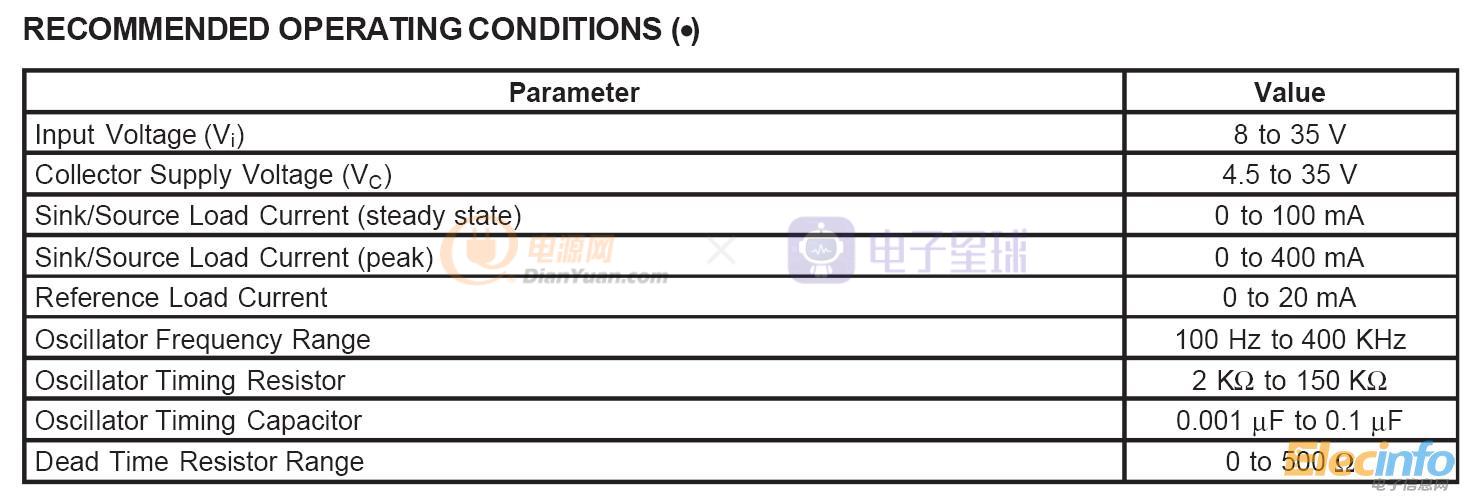

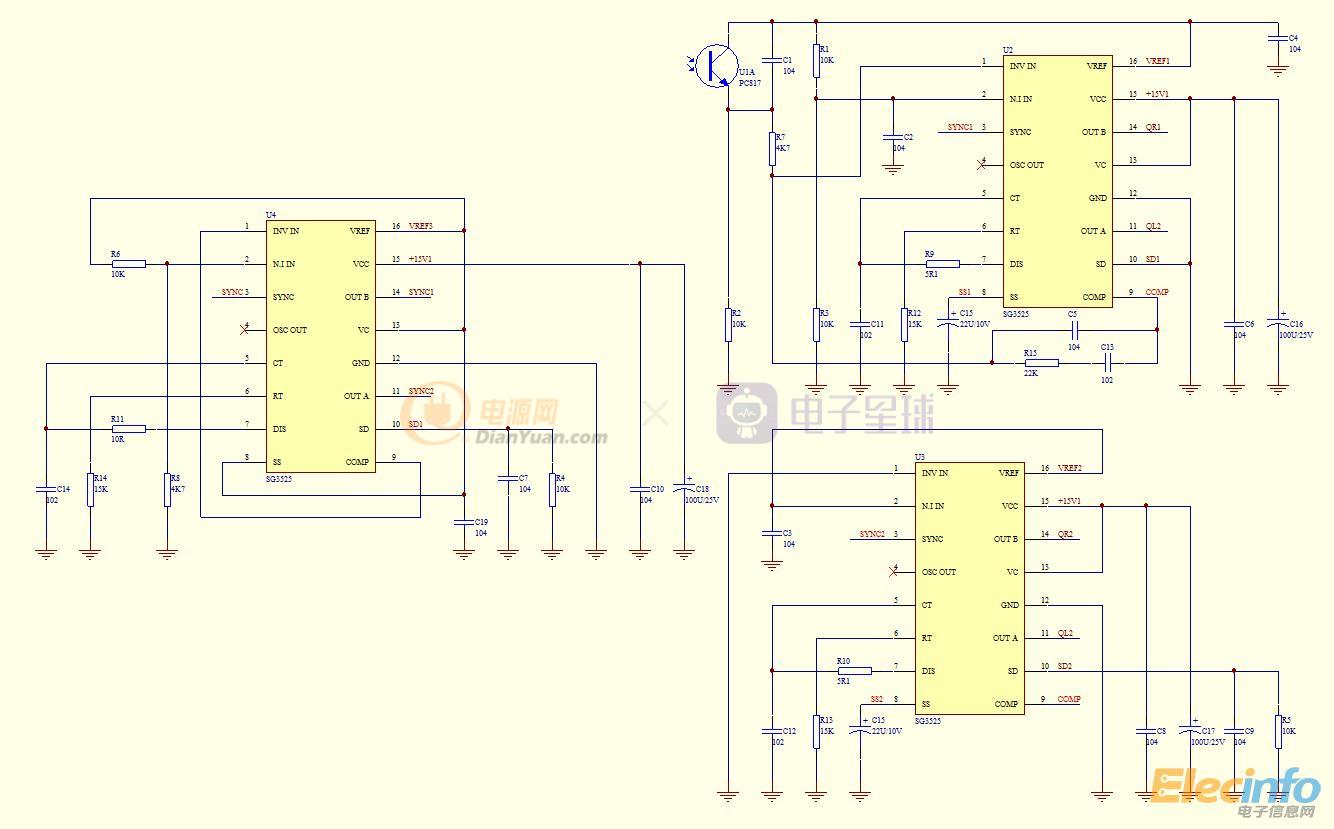

先上交錯控制部分的電路圖,說說交錯的核心。

主路的PWM控制

副路的PWM控制

本質上2路PWM是可以部分主和副的。但為了節省外置運放反饋,利用其中一個PWM控制器內部的運放作為反饋。同時,為了實現在輕載降頻的同時關閉其中一路PWM來減小待機功耗,所以在這里就分了主副來區分。

2路PWM的區別:

1. COMP端直接并聯

2. SS端分開

3. SD端分開,且主路SD直接屏蔽掉。

4. CT/RT/DIS同樣參與開關頻率的設置。

5. 主路的內部差分運放實現反饋,副路的內部運放直接屏蔽掉。

一個一個的區別來講解:

1. COMP端直接并聯。

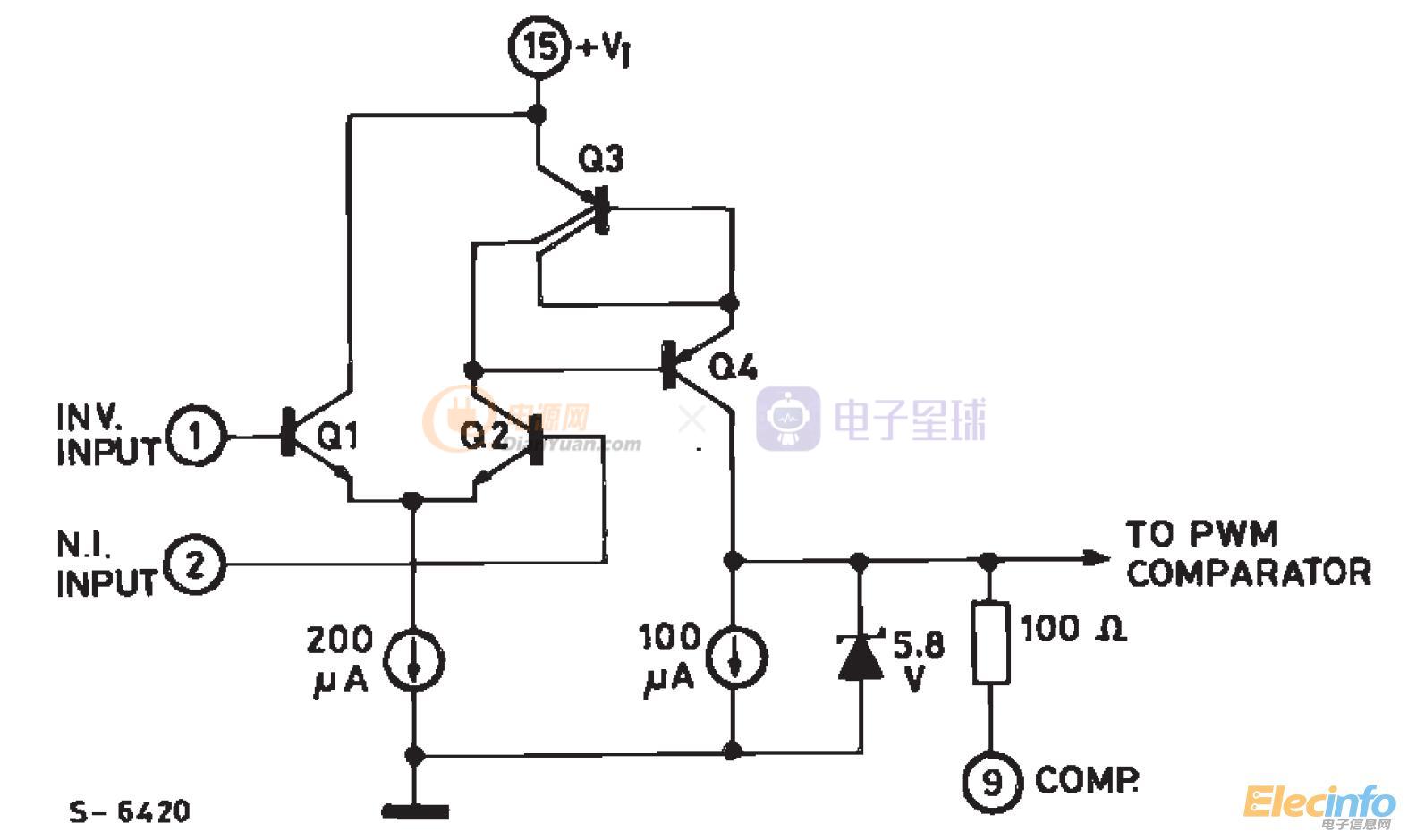

先貼一張SG3525的內部構造圖看看COMP端的的區域

從這里看,COMP端是內部差分運放的輸出端,由于采用的是主路的內部運放負反饋的方式,所以要讓副路的內部運放屏蔽的同時令其輸出高電位,通過負反饋下來來實現控制。

再看看COMP端的詳細構造:

在COMP端內部,并不是差分運放直接輸出到COMP,而是串聯了一只100R的電阻。

這個電阻帶來的問題是主負路的TO PWM COMPARATOR會出現很小的差異,等效為主路是差分運放直接輸出到主路的內部TO PWM COMPARATOR,而副路的則需要通過1個100R的電阻到達并聯的COMP端后再通過1個100R的電阻到達內部的TO PWM COMPARATOR,2個100R的電阻上會產生一個小小的壓降,實際表現為在閉環狀態是主副路的占空比會有很小的差異。但這對準開環架構的逆變器沒有任何影響。

當然,如果是做閉環架構,建議還是用外置運放來同時控制2路的COMP端,這樣能保持2路的PWM占空比盡量一致(2個3525內部運放本身的誤差忽略的情況下)。

2. SS端分開

實際實驗在控制3525保護時,直接控制SD端會導致恢復時非常大的電流沖擊,從而導致功率MOS瞬間炸管。原因是因為直接關閉SD端后再次開啟時3525是直接輸出最大占空比的,這個瞬間是不受控的。

所以,我通過關閉SS端來實現保護,再次開啟時會進入軟啟動狀態,大大緩解了對功率MOS的電流沖擊。在軟啟動時,即使2路的PWM軟啟有20%的時序誤差影響也不大。

2路分開以后,就可以實現在輕載或空載時關閉其中1路,實現低的待機的同時,再次開啟時也是軟啟動的。

3. SD端分開,且主路SD直接屏蔽掉。

上面已經說了保護是通過SS端來實現的,那么主路就不需要再強制關閉了,所以主路的SD端直接接地屏蔽掉,而副路的SD端需要用來在輕載時強制關閉。

4. CT/RT/DIS同樣參與開關頻率的設置:

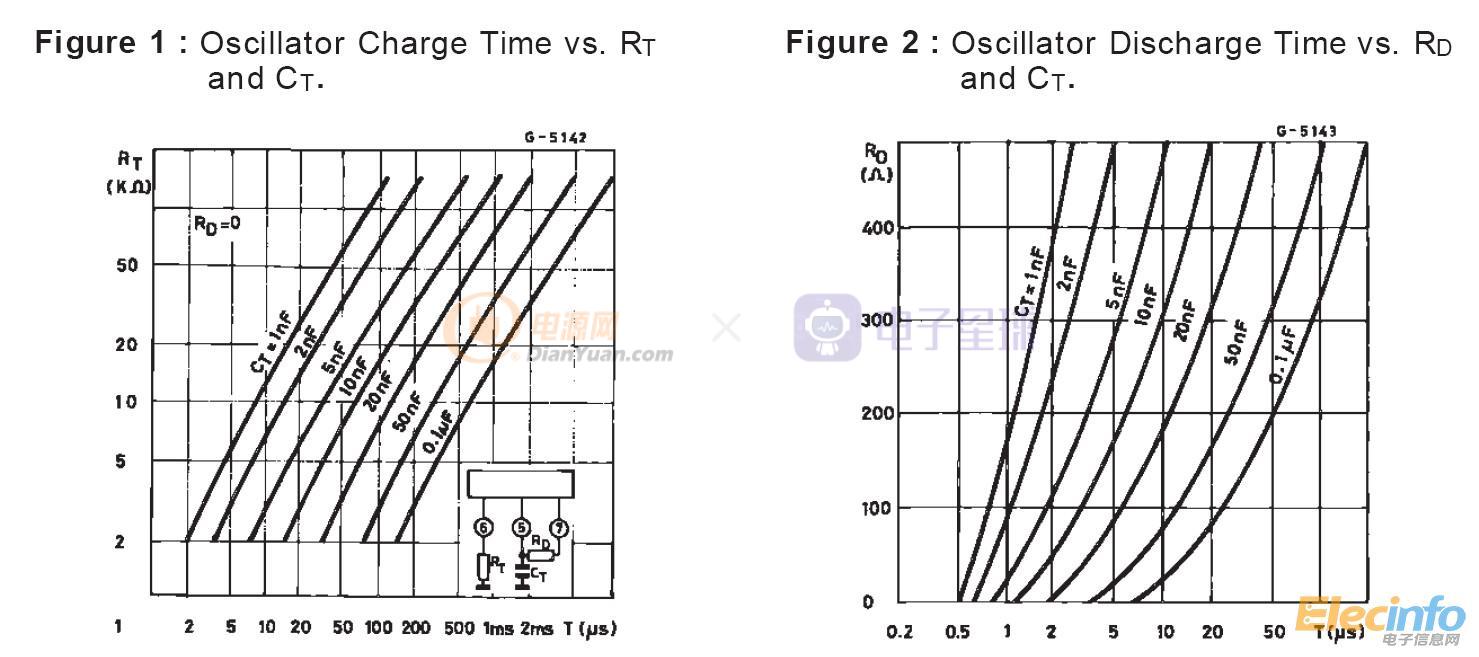

先貼2張CT/RT/RD的曲線

在規格書給出的曲線中,我們可以看出以下幾個問題:

在規格書給出的曲線中,我們可以看出以下幾個問題:

1. 即使RD=0,死區時間也不為0。

2. 推薦的最小震蕩電容CT=1nF。

3. 在CT=1nF,RD=0時,死區時間最短,為0.5uS。

在開環狀態下,需要追求最大占空比,所以這里的CT=1nF,RD可以適當選取小點的阻值,這里我用5.1R。

設定的頻率由下面的公式計算得來:

由于震蕩頻率與交錯的同步頻率有關,所以RT的取值在后面的同步頻率的計算中再來計算。

5. 主路的內部差分運放實現反饋,副路的內部運放直接屏蔽掉。

看了第1點這個就應該清楚了吧。

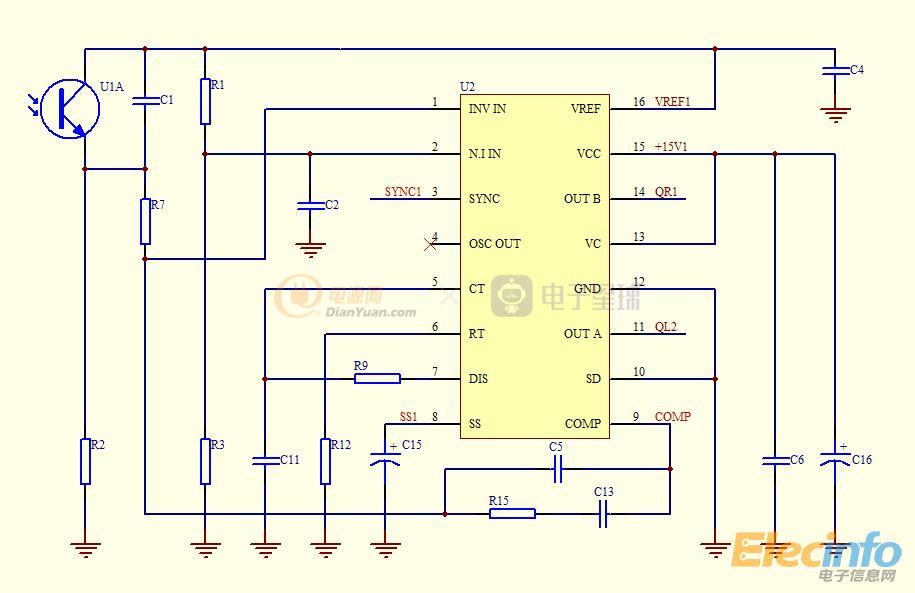

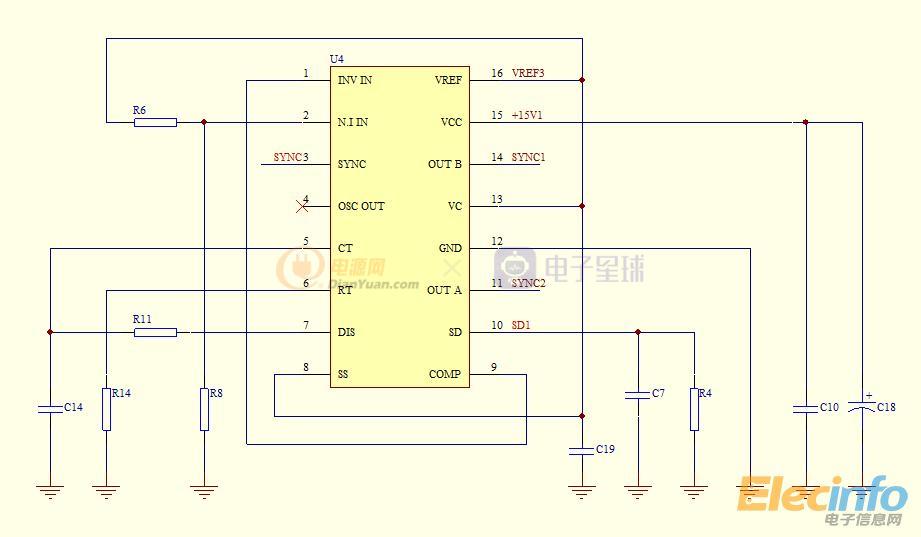

下面再上交錯信號源的SG3525電路:

這里有以下幾個特點:

1. SD1端可控。

2. 內部差分運放連接為跟隨器形式。

3. SYNC端預留。

4. CT/RT/DISS(RD)設置震蕩頻率。

5. VC端接VREF。

6. OUT A/B輸出到主副路的SG3525 SYNC端。

1. SD1用來關閉信號源,關閉后控制PWM的2個SG3525就是同步并聯的了,而且開關頻率不再受控于信號源,而是主副路SG3525的自身震蕩產生的PWM。在輕載時關閉副路的同時關閉交錯信號源的SG3525,可以降低開關頻率,進一步減小功耗。

2. 內部差分運放連接為跟隨器的形式,COMP端的的電壓,COMP端的電壓決定了OUT A/B端的PWM輸出占空比。所以通過設置P2 端的R5和R8就可以控制輸出的占空比大小。在此得吐槽一下SG3525的SYNC端對輸入信號占空比的要求,真是有點高。

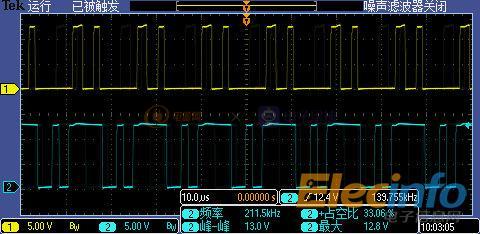

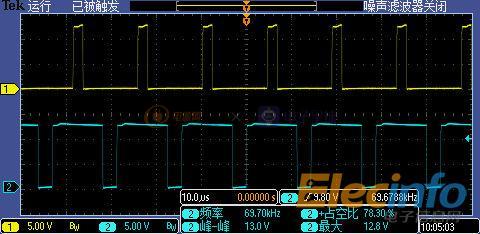

同步端的交錯信號占空比太小后就無法同步了,不受控與同步端了;同步端的交錯信號占空比太大后,輸出的PWM就亂了,如下圖:

經過反復的實驗得出,要實現同步,同步信號的占空比必須控制在3%~12%之間。

而且在12-13%時會出現混亂,現象如下圖:

所以,這里取折中,設置占空比在6-8%,再來看看輸出PWM端的波形:

控制主路SG3525的差分運放來減小占空比,波形如下:

再減小。

到此,交錯同步的問題得到完美解決。

3. SYNC端預留。

這個是用來實現級聯的,也就是說:可以再擴展為4相交錯甚至8相交錯(8相交錯時需要降低開關頻率)

4. CT/RT/DISS(RD)設置震蕩頻率。

這里再來講講3個SG3525的震蕩頻率設置的講究。

SG3525的同步頻率要是被同步IC的震蕩頻率的1.3倍以上,是輸出的開關頻率2.6倍以上才能正常穩定的工作。所以要使開關頻率在35KHz左右,交錯信號源的SG3525的輸出頻率為70KHz左右,其震蕩頻率就需要140Khz左右,同時,主副路的SG3525的震蕩頻率要為同步頻率的1/1.3,即53.8KHz左右,這里取50KHz,頻率根據59帖的公式計算即可。

高清大圖貼上交錯控制單元的線路圖和參數:

5. VC端接VREF。

因為主副路的SG3525 SYNC端識別的高電平為5V就可以了,所以這里把交錯信號源的SG3525的輸出供電端接到了自身的基準5.1V上。

6. OUT A/B輸出到主副路的SG3525 SYNC端。

交錯信號源的輸出信號作為主副SG3525的震蕩頻率,從而控制PWM的輸出頻率。