FPGA中的細粒度和粗粒度

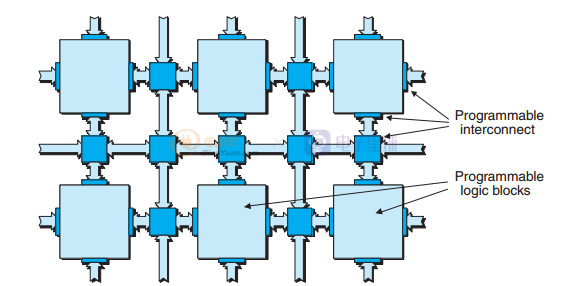

通常將FPGA產品劃分為細粒度或粗粒度。這兩個詞是什么意思呢?首先,我們需要提醒自己,FPGA與其他器件的主要區別是,它們的底層結構主要由大量相對簡單的“可編程邏輯塊”組成,這些塊鑲嵌在可編程互連的結構中。

在細粒度的架構下,每個邏輯塊只能實現一個非常簡單的功能。例如實現一個三輸入函數邏輯塊。

而在粗粒度的架構下,相比于細粒度架構,每個邏輯塊都包含大量的邏輯。例如,一個邏輯塊可能包含四個4輸入的LUTs、四個多路復用器、四個d型觸發器和一些快速進位邏輯。

關于架構粒度的一個重要考慮事項是,與這些塊支持的功能數量相比,細粒度實現需要進入和退出每個塊的連接數量相對較大。當塊的粒度增加到中粒度或更高時,與它們能夠支持的功能相比,進入塊的連接數量會減少。這是很重要的一個權衡點,因為當信號通過FPGA傳播時,可編程的塊間互連處理了絕大多數與信號相關的延遲任務。

這兩個架構各有優缺點。細粒度FPGA的邏輯功能塊一般較小,僅由很小的幾個晶體管組成,非常類似于半定制門陣列的基本單元,其優點是功能塊的資源可以被完全利用,缺點是完成復雜的邏輯功能需要大量的連線和開關,因而速度慢;粗粒度FPGA的邏輯塊規模大,功能強,完成復雜邏輯只需較少的功能塊和內部連線,因而能獲得較好的性能,缺點是功能塊的資源有時不能被充分利用。

邏輯塊(Logic Blocks)

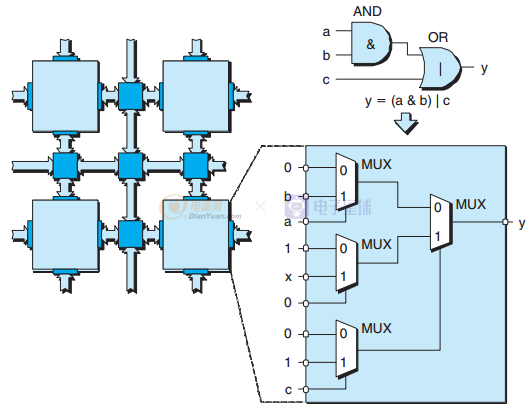

可編程邏輯塊有兩種基本形式:基于MUX(多路復用器)和基于LUT(查找表)。

基于MUX。作為基于mux的方法的一個例子,考慮一種方法3輸入函數y (a & b) |c可以用一個只包含多路復用器的塊來實現。

可以對設備進行編程,使對該塊的每個輸入都用邏輯0、邏輯1或來自另一個塊或設備主輸入的信號(a、b或c)的1或0表示。這允許以無數種方式配置每個塊,以實現大量可能的功能。

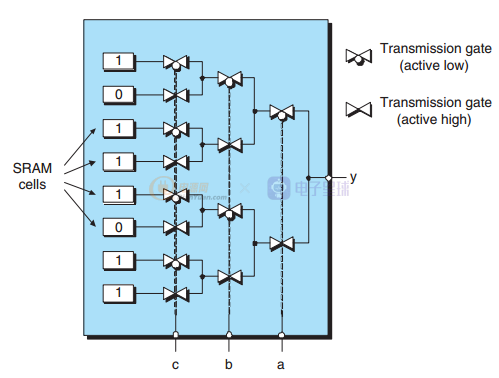

基于LUT。LUT背后的基本概念相對簡單。一組輸入信號用作查找表的索引(指針)。該表的內容被安排為每個輸入組合指向的單元格包含所需的值。例如,我們假設我們希望實現這個函數:

y=(a&b)|c

這可以通過加載一個具有適當值的3輸入LUT來實現。為了下面的例子的目的,我們假設LUT是由SRAM單元形成的(也可以使用反熔絲、E2PROM或Flash單元形成)。一種常用的技術是使用如圖所示的級聯傳輸門來選擇所需的SRAM單元。以配置的目的將它們連接在一起——也就是說,用所需的值加載它們。

如果傳輸門被激活,它將在輸入端看到的信號傳遞到輸出端。如果柵極被禁用,它的輸出與它驅動的電線是電斷開的。傳輸門的符號顯示一個小圓圈,表明這些門將被一個邏輯0在他們的控制輸入激活。相比之下,沒有圓圈的符號表示這些門將被邏輯1激活。基于這種理解,很容易看到如何使用不同的輸入組合來選擇不同SRAM單元的內容。

這兩種架構的產品,都各有各有優勢。MUX架構在實現大量獨立小微邏輯功能時,大大的增加了硅利用率,以及編程效率。LUT則在實現小功能時會占用整個LUT單元,導致浪費。而LUT架構在很多器件中,也能通常被用作小塊RAM,提高了靈活性。

后面將會著重繼續深入邏輯塊方面的介紹。