為了提高電源的效率和功率密度尤其是低輸出電壓的應用場合,同步整流是不可或缺的。

圖1-1 反激輸出二極管損耗

比如上圖的反激電源如果輸出二極管Vf=0.7V ,輸出電壓Vout=3V則效率不會高于3/(3+0.7)=81%。

為了提升效率一般會選用低導通壓降的肖特基二極管,相對于肖特基二級管采用同步整流可以進一步提升效率。

圖1-2 普通二極管、肖特基二極管及同步整流的對比

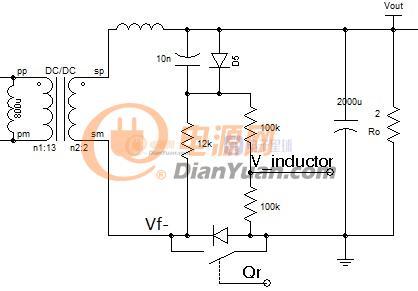

先以隔離反激同步整流為討論目標,反激的儲能電感就是變壓器本身其波形特性如下:

圖1-3 反激輸出二極管Vf+端波形

仿真參數:變壓器匝比n=6.5:1,輸入電壓100V 、輸出電壓12V、二極管導通壓降0.7V、開關頻率60kHz。

上述波形中的Vf+是圖1中輸出二極管的陽極波形,在Ton時刻受輸出電壓鉗位Vf+=12+0.7=12.7V ,在Toff時刻輸入電壓通過變壓器折算到次邊Vf+=-100/6.5=-15.38V (因漏感的分壓作用實際仿真值為-14.92V)。這個Vf+近似的反映了電感兩端的電壓變化情況,因而可以用此電壓來構建和模擬伏秒平衡時的電流狀態,從而實現對電流的預判斷。

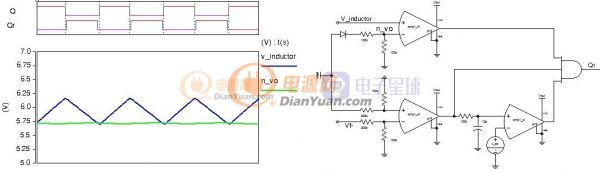

圖1-5中的模擬電感電流是一種鏡像的交流信號處理起來有些麻煩,所以把積分電路變換成另一種形式。

圖1-6 RC積分電路 2

同步整流是對開關管進行操作時間為nS級的所以控制電路中沒有采用運算放大器都只是高速比較器,鏡像操作如上圖將積分電阻、電容互換位置即可。不過這種操作后參考點變成了Vout,通過二極管D5鉗位。

另外初步將同步整流管放置在低邊,這樣驅動會簡單些不過EMI共模噪音會差些。

穩態時同步整流驅動信號Qr的產生可分下面兩部分:

一、 延遲開啟

圖1-6中的輸出二極管陰極Vf-端的信號和初級MOS驅動信號Q近似同步

圖1-7 輸出二極管陰極Vf-信號

以Vf-信號為參考增加一小段延遲(死區時間)就可以得到延遲開啟的Qr信號。

二、 提前關閉

通過比較模擬的電感電流信號V_inductor和輸出Vout信號來實現提前關閉同步信號的功能。

綜合一、二兩點得出穩態CCM模式時的同步驅動Qr信號如下:

圖1-8 穩態CCM模式Qr信號及產生電路

反激的伏秒平衡公式為Uin*Ton/Lm =Uo*Toff/Lm簡化后Uin*Don =Uo*Doff,最后推出Uo=Uin*Don/(1-Don)(在BCM或CCM模式下)。

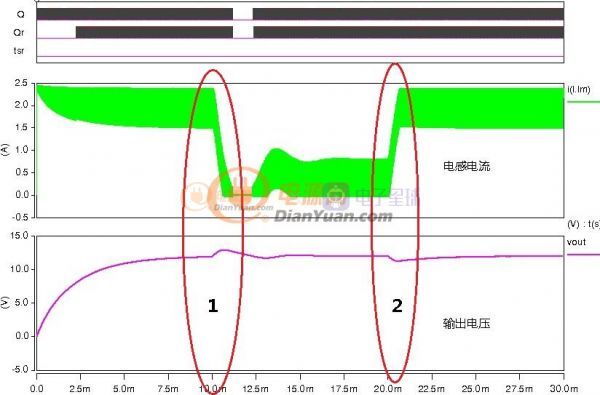

在電源剛上電時,輸出電壓Uo從零開始逐漸上升至設定電壓值,這個過程中若要維持伏秒平衡則Toff的時間將遠大于開關周期,對于定頻控制模式這是無法實現的所以在此階段伏秒無法滿足平衡。

圖2-1 上電伏秒不平衡波形

上圖中由于伏秒不平衡電感電流要比穩態時的高(電路有做限流處理),模擬電感電流也超出了n_vo信號的范圍,同步信號Qr失控。圖中的tsr信號表Q同Qr信號相與的操作,用來檢驗原邊及同步信號是否同時導通,正常情況tsr信號應恒為低電平。

要實現任意情況下都“滿足”伏秒平衡成立,根據伏秒平衡公式有兩種方法:

方法1、在開關周期上做文章

這種方法是強制令信號Q+Qr<=T(Q、Qr這里分別為原邊及同步MOS的導通時間,T為開關周期),這樣即使輸出電壓Uo=0也可以推算出同步整流信號Qr的最大導通時間以避免出現同時導通的情況。

具體實施方法是由Q信號(實為Vf-信號)觸發周期≤T的計時器電路作為次邊同步MOS的關斷信號,這種方法只針對臨界和連續模式在斷續模式下不受影響。另外增加了欠壓保護功能,仿真效果如下:

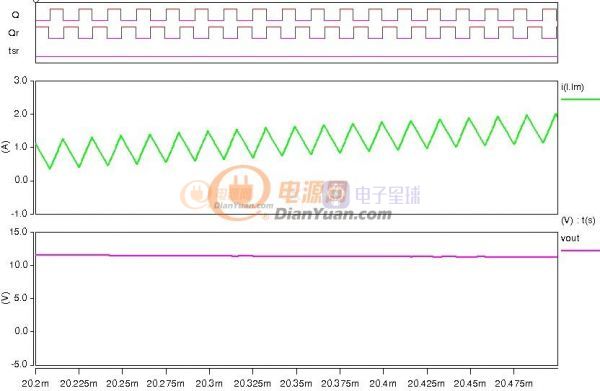

圖2-2-1 周期法啟動及動態波形

按照周期法做的仿真在啟動、滿載到輕載、輕載到滿載過程中都沒由出現同時導通的情況(tsr信號恒為低電平)。

對圖中圈1和圈2做局部放大如下:

圖2-2-2 周期法滿載到輕載突變局部放大圖

圖2-2-3 周期法輕載到滿載突變局部放大圖

從仿真結果看,周期法是可以解決連續模式、大動態負載下的同步整流控制問題。但周期法也有局限性需要根據主開關的工作頻率來精確設置同步整流管的工作頻率,在變頻模式中無法使用或是性能達不到最佳。

在對這種Vout法做極限測試時發現了幾個問題,其中之一就是這種Vout法存在次諧波震蕩的隱患。

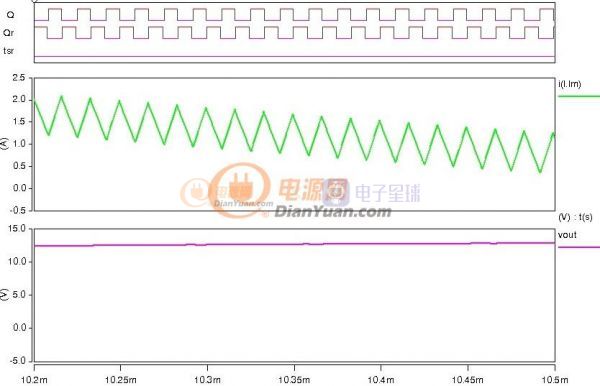

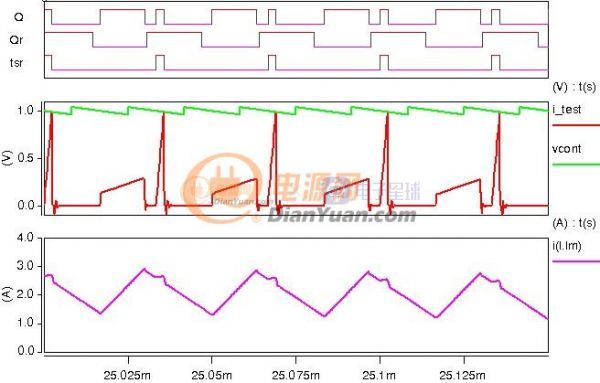

當初級側電流采樣電阻取R=0.3時電路工作正常,波形如下:

圖3-1 R=0.3正常波形

當取采樣電阻取R=0.1時發生了次諧波震蕩,

圖3-2 R=0.1次諧波震蕩波形

這里的次諧波震蕩與電流模式(CCM、Don>0.5)反激略有不同,在前一個周期輸入向輸出傳輸能量,后一個周期輸出向輸入傳輸能量(電流斜率由次級漏感決定),其它方面比較相似。發生次諧波震蕩時輸出電壓低于設定的12V。

消除次諧波震蕩可以加斜坡補償或者令占空比Don<0.5,圖3-2是有加斜坡補償的只是補嘗的太少。圖3-1中最大占空比上限為Donmax=0.8,但是并沒有發生次諧波震蕩,那么次諧波震蕩的臨界條件是什么呢?